Class meets Monday, Wednesday, 12.15–14.00

in room A.121. Friday classes

will be held as needed at the same time in A.121, to make up in case of instructor's

absence during regular class meeting times. | No lecture on Wednesday, Oct. 8

| | ||||

Class meets Monday, Wednesday, 12.15–14.00

in room A.121. Friday classes

will be held as needed at the same time in A.121, to make up in case of instructor's

absence during regular class meeting times. | No lecture on Wednesday, Oct. 8

| | ||||

| Class | Topic | Slides | Reading list | Assignments |

| 22/9 | Welcome and introduction | Slides | Chapter 1 (1.1-1.3) from course textbook | |

| 24/9 | Metrics | Slides | Chapter 1 (1.4-1.12) from course textbook | |

| 29/9 | Pipelining review | Slides | Appendix A (A.1-A.3) from course textbook | |

| 1/10 | Pipelining review | Handouts from 14/10 | Homework 1 | |

| 6/10 | Dynamic scheduling with Scoreboard | Slides | Section 2.1, Appendix A (A.5, A.7,A.8) from course textbook | |

| 8/10 | Dynamic scheduling with Scoreboard | Handouts from 23/10 | ||

| 13/10 | Dynamic scheduling with Tomasulo | Slides | Chapter 2 (2.4,2.5) from course textbook | |

| 15/10 | Dynamic scheduling with Tomasulo | Handouts from 25/10 | Tomasulo's original paper | |

| 20/10 | ILP and Static scheduling | Slides | Section 2.2, Appendix G(G.1-G.3) from course textbook | Homework 2 |

| 22/10 | Branch prediction | Slides | Sections 2.3, 2.9 (pages 121-126), Appendix G(G.4) from course textbook. Alternative implementations of two-level adaptive branch predictors | |

| 29/10 | Precise Exceptions and Speculation | Slides | Appendix A(A.4), Section 2.6, Section 2.9 (pages 127-129) from course textbook | |

| 3/11 | Precise Exceptions and Speculation | Handouts from 13/11 | Programming Assignment 1 | |

| 5/11 | Multiple issue processors (Superscalar and VLIW) | Slides | Sections 2.7, 2.8, Appendix G.3(G-19 to G-21), Appendix G.6 | |

| 10/11 | Thread-Level Parallelism (TLP) | Slides | Sections 3.5, 3.6,Simultaneous Multithreading: Maximizing On-Chip Parallelism, Tullsen, Eggers and Levy, ISCA'95, Power5 System Microarchitecture, Sinharoy et. al, IBM Journal of Research and Development, 49(4–5), September 2005. | |

| 26/12 | Cache memories: Design and performance analysis | Slides | Section 5.1, Appendix C.1 | |

| 1/12 | Cache memories | Handouts from 1/12 | Homework 3 | |

| 3/12 | Cache design optimizations | Slides | Appendix C.2, Section 5.2 | |

| 8/12 | Cache design optimizations | Handouts from 3/12 | ||

| 10/12 | Virtual memory | Slides | Appendix C.4 | Programming Assignment 2 |

| 15/12 | Main Memory | Slides | Chapter 7, Sections 7.1–7.5, from textbook Memory Systems: Cache, DRAM, Disk, by Bruce Jacob, Spencer W. Ng, and David T. Wang | |

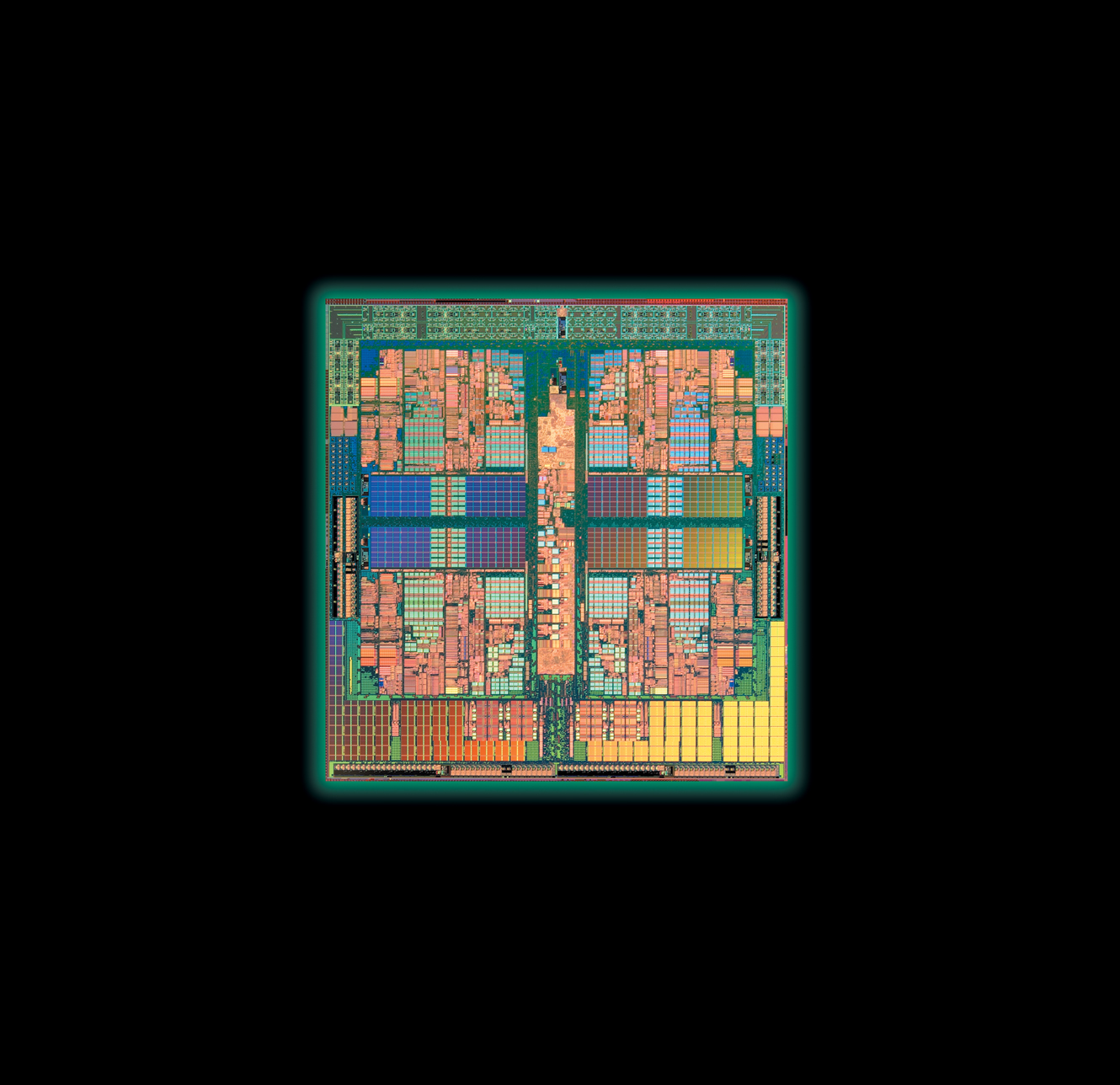

| 17/12 | Multi-core Processors (Basics) | Slides | Chapter 4 |