| Class | Topic |

Slides |

Reading list |

Assignments |

| 7/10 |

Welcome and introduction | Slides |

Chapter 1 (1.1-1.3) from course textbook |

|

| 9/10 |

Metrics |

Slides |

Chapter 1 (1.4-1.12) from course textbook |

|

| 14/10 |

Pipelining review |

Slides |

Appendix A (A.1-A.3) from course textbook |

|

| 16/10 |

Pipelining review |

Handouts from 14/10 |

|

Homework 1 |

| 23/10 |

Dynamic scheduling with Scoreboard |

Slides |

Section 2.1, Appendix A (A.5, A.7,A.8) from course textbook |

|

| 25/10 |

Dynamic scheduling with Scoreboard |

Handouts from 23/10 |

|

|

| 28/10 |

Dynamic scheduling with Tomasulo |

Slides |

Chapter 2 (2.4,2.5) from course textbook |

|

| 30/10 |

Dynamic scheduling with Tomasulo |

Handouts from 25/10 |

Tomasulo's original paper |

|

| 4/11 |

ILP and Static scheduling |

Slides |

Section 2.2, Appendix G(G.1-G.3) from course textbook |

Homework 2 |

| 6/11 |

Branch prediction |

Slides |

Sections 2.3, 2.9 (pages 121-126), Appendix G(G.4) from course textbook.

Alternative implementations of two-level adaptive branch predictors |

|

| 13/10 |

Precise Exceptions and Speculation |

Slides |

Appendix A(A.4), Section 2.6, Section 2.9 (pages 127-129) from course textbook |

|

| 18/11 |

Precise Exceptions and Speculation |

Handouts from 13/11 |

|

Programming Assignment 1 |

| 20/11 |

Multiple issue processors (Superscalar and VLIW) |

Slides |

Sections 2.7, 2.8, Appendix G.3(G-19 to G-21), Appendix G.6 |

|

| 25/11 |

Thread-Level Parallelism (TLP) |

Slides |

Sections 3.5, 3.6,Simultaneous Multithreading: Maximizing On-Chip Parallelism, Tullsen, Eggers and Levy, ISCA'95, Power5

System Microarchitecture, Sinharoy et. al, IBM Journal of

Research and Development, 49(4–5), September 2005.

|

|

| 27/11 |

Preparation for midterm |

Slides |

|

|

| 4/12 |

Cache memories: Design and performance analysis |

Slides |

Section 5.1, Appendix C.1 |

Homework 3 |

| 9/12 |

Cache design optimizations |

Handouts from 1/12 |

|

|

| 11/12 |

Cache design optimizations |

Handouts from 9/12 |

|

|

| 16/12 |

Virtual memory |

Slides |

Appendix C.4 |

Programming Assignment 2 |

| 20/12 |

Main Memory |

Slides |

Chapter 7, Sections 7.1–7.5, from textbook Memory Systems:

Cache, DRAM, Disk, by Bruce Jacob, Spencer W. Ng, and David T. Wang |

|

| 17/1 |

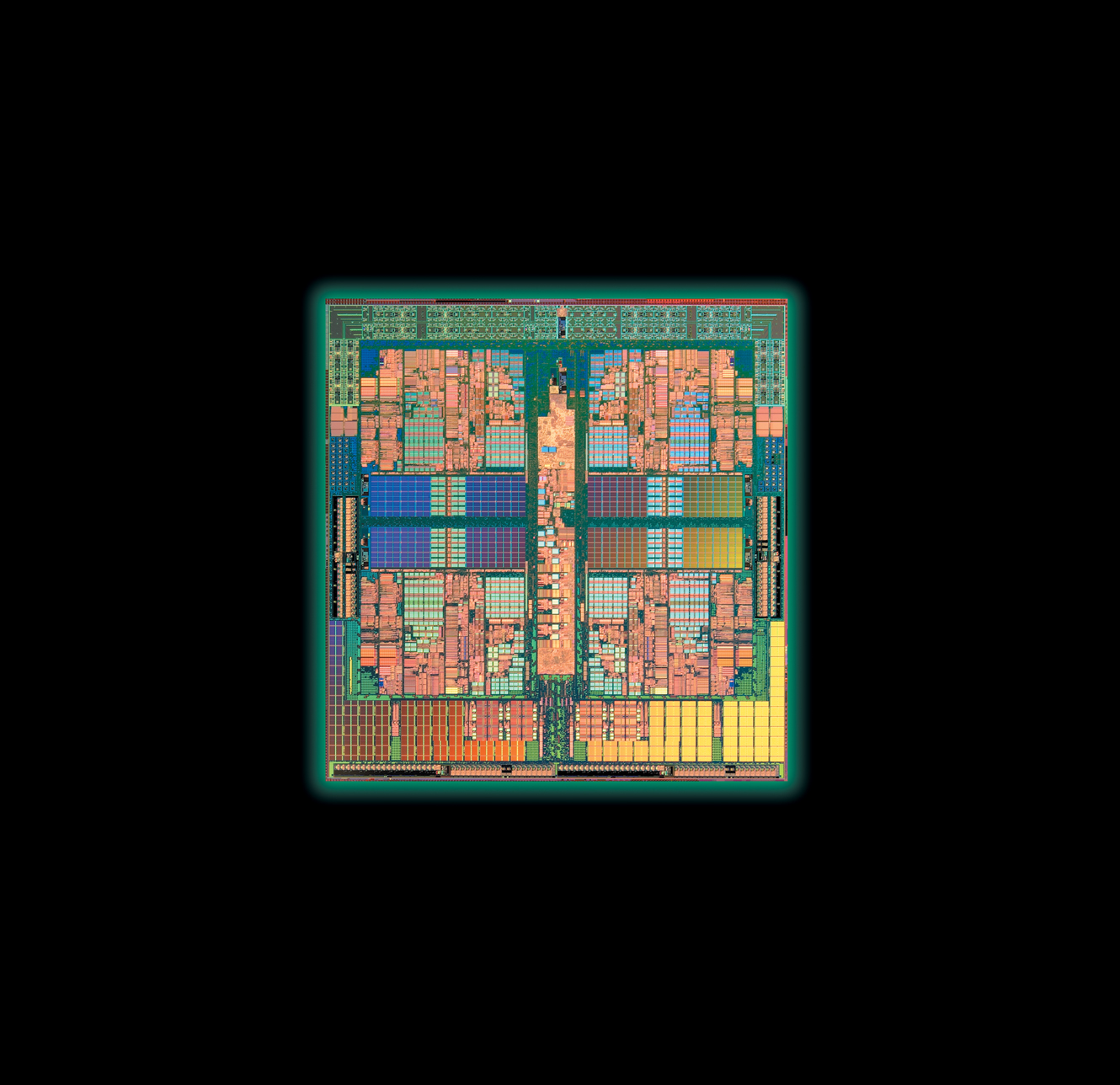

Multi-core Processors (Basics) |

Slides |

Chapter 4 |

|

I. Mavroidis - Last Modification - 2/11/2013.