## 3.1 The need for multiple queues within a same buffer memory: Multi-Queue Data Strucutres

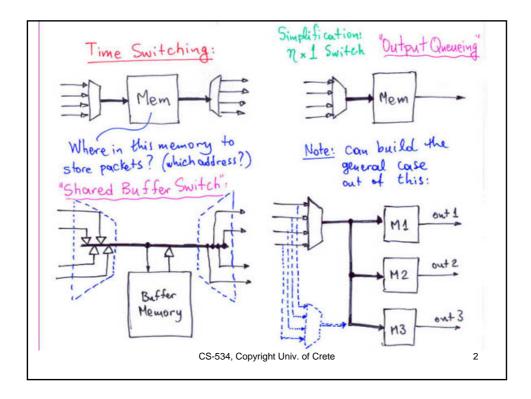

- Buffers memories for time switching: what data structures?

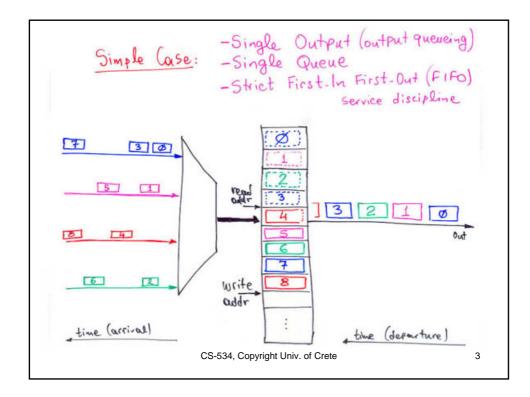

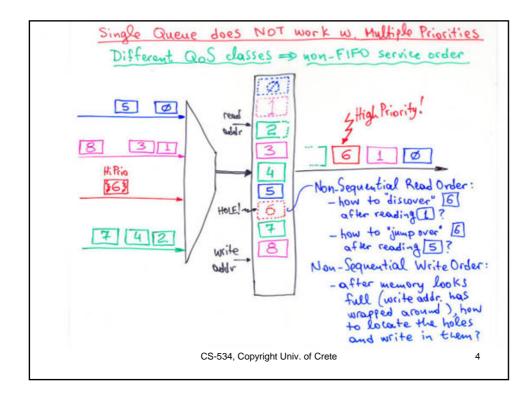

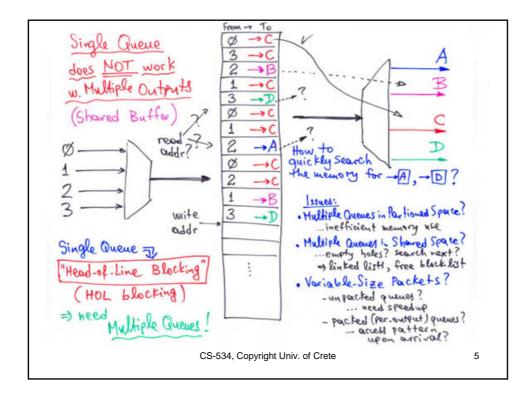

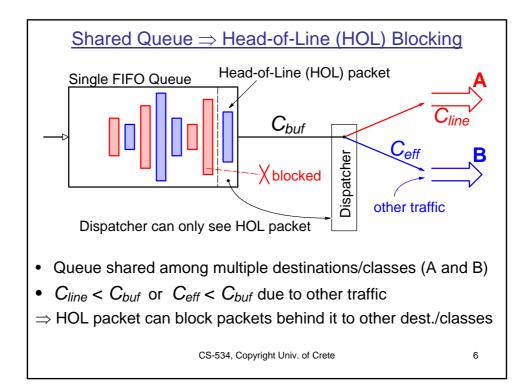

- Single queue feeding multiple destinations/classes

⇒ Head-of-Line (HOL) Blocking ⇒ poor performance

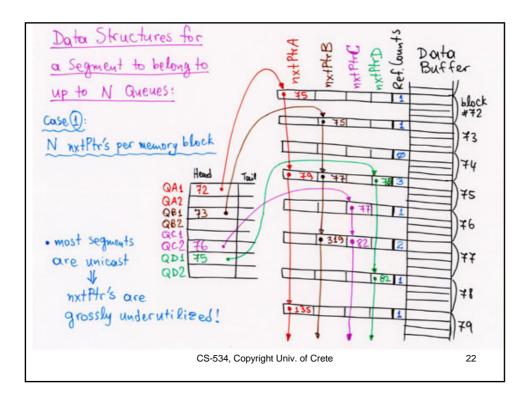

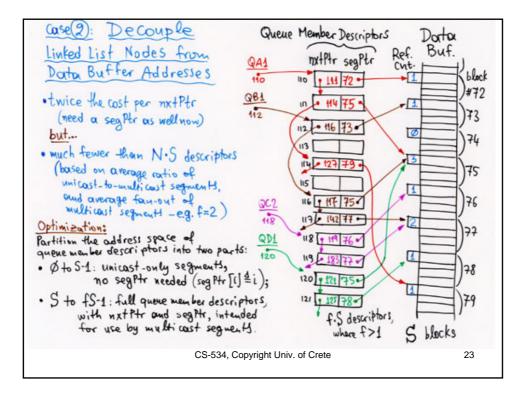

- Multiple Queues in one buffer:

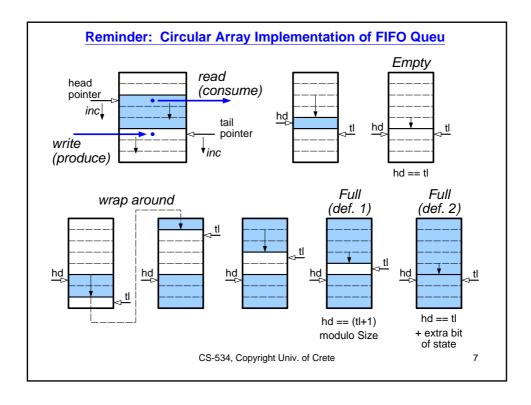

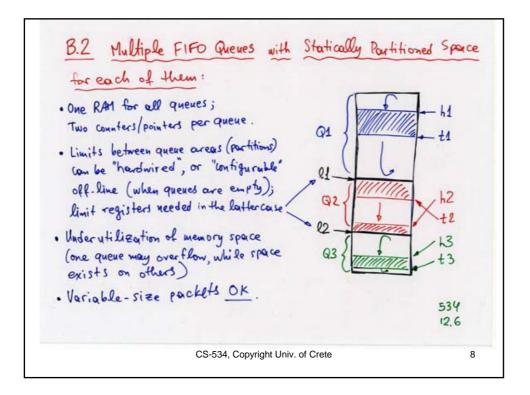

- Partitioned Space (underutilized)  $\Rightarrow$  circular queues

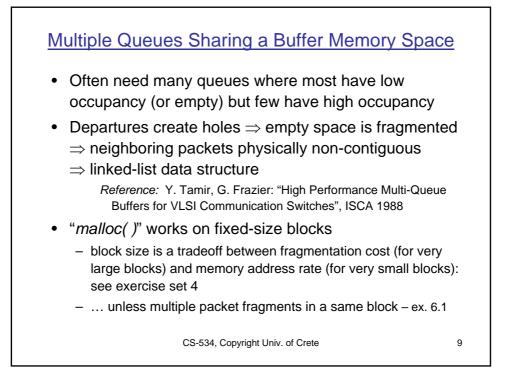

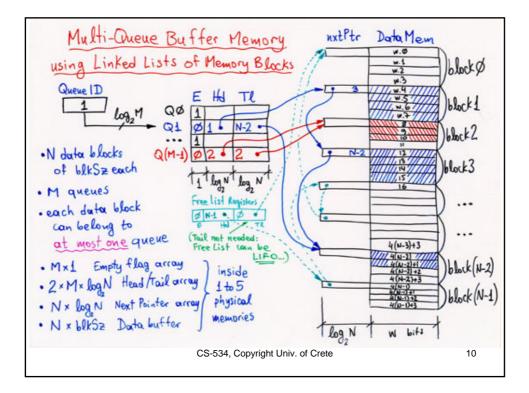

- Shared Space (efficient)  $\Rightarrow$  linked-list queues

CS-534, Copyright Univ. of Crete

1

| Assumptions:<br>"off-chip" means                               | E                 | Hd                      | TL                     | NxtPtr                 | Latany<br>(clock)<br>(cycles) | Thruput<br>( <u>op's</u> ) | Latency<br>(clect)<br>(cycles) | Thrupit<br>(op's) |

|----------------------------------------------------------------|-------------------|-------------------------|------------------------|------------------------|-------------------------------|----------------------------|--------------------------------|-------------------|

| ang/deg controller FSM                                         |                   |                         | single,<br>thip me     |                        | 4.5                           | 1 4 = 5                    | 5                              | 1<br>5 or 4       |

| on separate chips<br>"on-chip" means all together              | 1-port<br>on-chip | off.                    | single,<br>chip m      | 1-port<br>nemors       | 4                             | 1/4                        | 5                              | 1/4               |

| 1 memacc./cycle/port<br>off-chip dependent                     | s-tort<br>on-chip |                         | off-chip<br>wide       | 1-port<br>off-chij     | 3*                            | 1/3                        | 5                              | 1/3               |

| accesse's (read, then<br>use data as mext<br>address) Cost one | 1-Port<br>on-chip | J-port<br>off-<br>chilt | 1-port<br>off-<br>chip | 1-port<br>off-chir     | 3*                            | 1/2                        | 5                              | 1/2               |

| extra cycle of latency between them                            | 1-port<br>Ou-chip | 1-port<br>DM-chil       | J-Port<br>ON-chi       |                        | 2*                            | 1/2                        | 3                              | 1/2               |

| Note:<br>* enqueue latency                                     | 2-port<br>on-chip | 2-port<br>on-chip       | 2. port<br>on-chip     | s-part<br>off-<br>chip | 2*                            | 1                          | 3                              | 1                 |

| may increase<br>when mixing enqueue                            | and de            | queue c                 | operatio               | ins in the             | same                          | Pipelin                    | e.                             |                   |

|                                                                | CS                | 8-534, Co               | pyright L              | Iniv. of Crete         |                               |                            |                                | 13                |