| CS-534: Packet Switch Architecture

Spring 2003 |

Department of Computer Science © University of Crete, Greece |

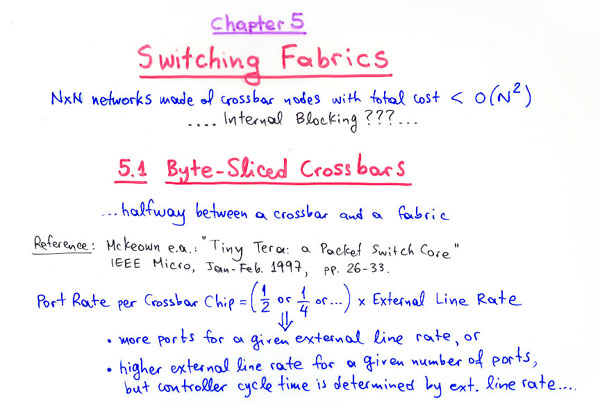

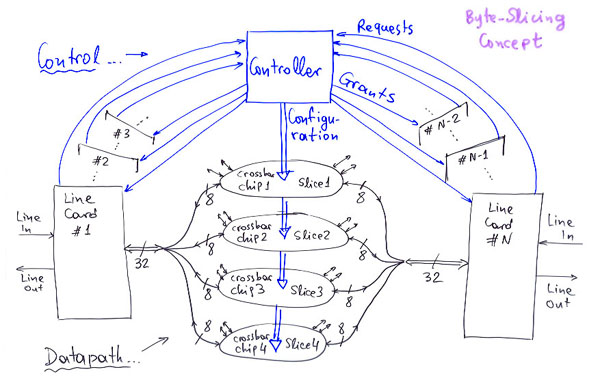

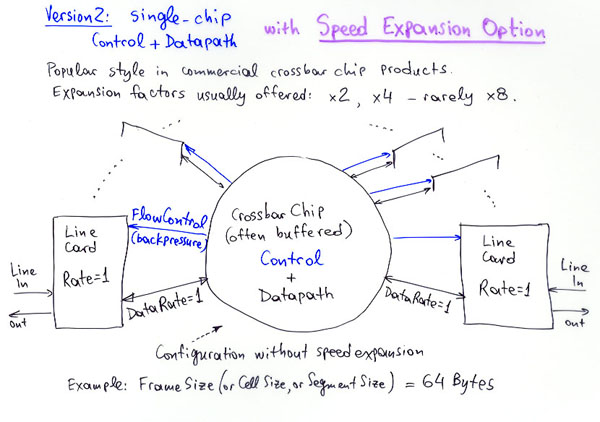

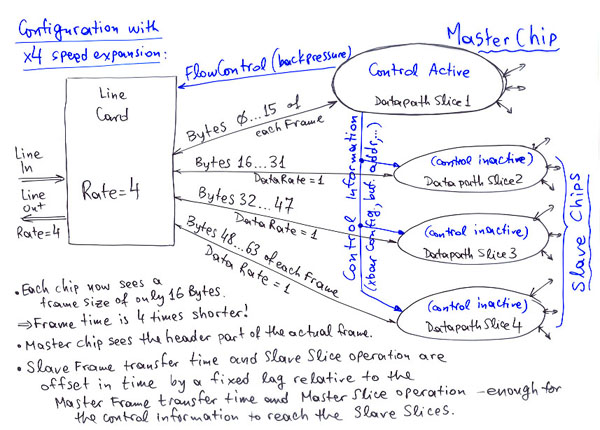

5.1 Byte-Sliced Crossbar Switches

|

[Up: Table of Contents] [Prev: 4.5 Int. Speedup - CIOQ] |

[Next: 5.2 Benes, Clos, Fat Trees] |

References:

|

[Up: Table of Contents] [Prev: 4.5 Int. Speedup - CIOQ] |

[Next: 5.2 Benes, Clos, Fat Trees] |

| Up to the Home Page of CS-534

|

© copyright

University of Crete, Greece. Last updated: 9 May 2003, by M. Katevenis. |