| CS-534: Packet Switch Architecture

Spring 2003 |

Department of Computer Science © University of Crete, Greece |

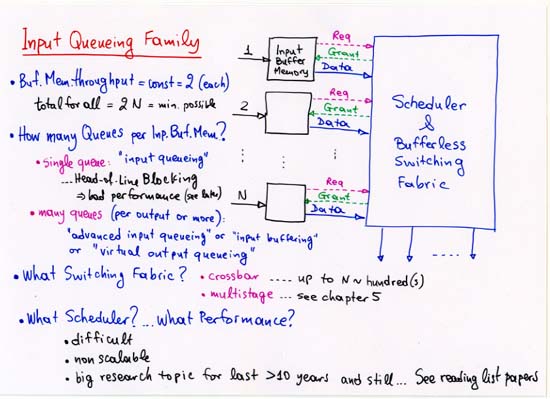

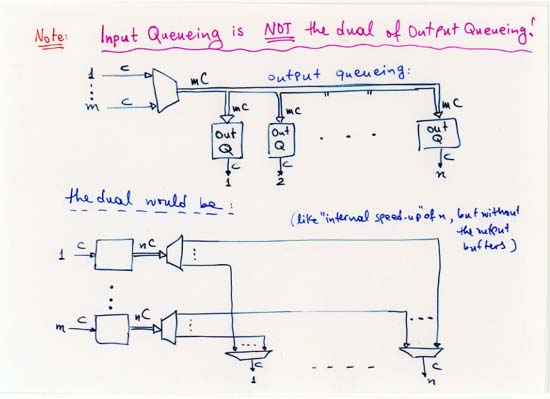

4.3 The Input Queueing Family

|

[Up: Table of Contents] [Prev: 4.2 Shared Buffer Impl.] |

[Next: 4.4 Crossbar Scheduling] |

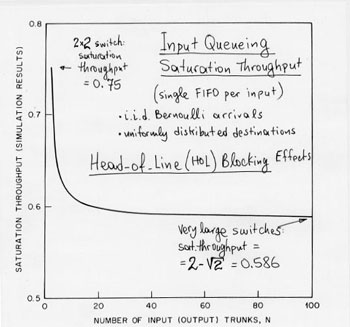

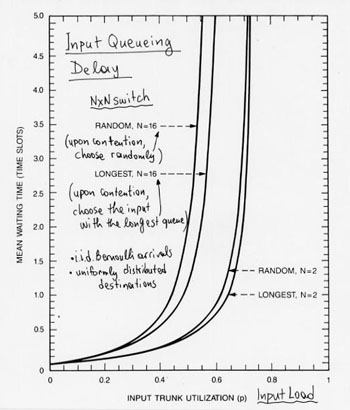

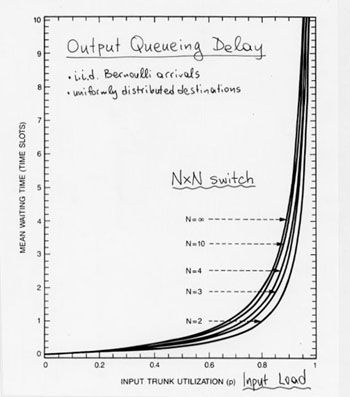

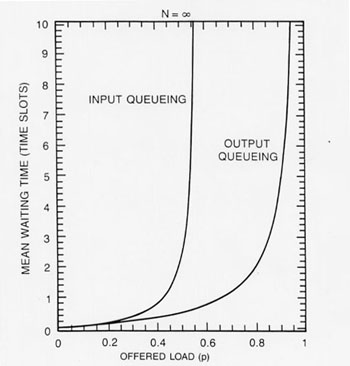

Throughput and Delay under Input Queueing with Head-of-Line (HOL) Blocking:

When the incoming traffic consists of fixed-size packets from independent, identically distributed (i.i.d.) Bernoulli processes, with uniformly-distributed destination (output) ports, analysis and simulation have yielded the results plotted below. Sources (© copyright IEEE):Attention: results derived for i.i.d. Bernoulli (non-bursty) arrivals, with uniformly-distributed destinations (no overloaded hot-spots), are only useful for gaining a rough, first insight into the behavior of systems, but are often not representative of the real behavior of systems under real traffic!...

© copyright IEEE

Appendices for optional study:

Performance analysis transparencies

by prof. George Stamoulis, CS-534, Spring 2000 semester:

|

[Up: Table of Contents] [Prev: 4.2 Shared Buffer Impl.] |

[Next: 4.4 Crossbar Scheduling] |

| Up to the Home Page of CS-534

|

© copyright

University of Crete, Greece. Last updated: 9 May 2003, by M. Katevenis. |