# **DRAM Technology**

- Data stored as a charge in a capacitor

- Single transistor used to access the charge

- Must periodically be refreshed

- Read contents and write back

- Performed on a DRAM "row"

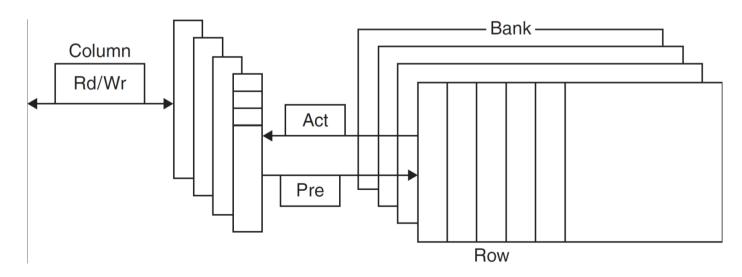

# **Advanced DRAM Organization**

- Bits in a DRAM are organized as a rectangular array

- DRAM accesses an entire row

- Burst mode: supply successive words from a row with reduced latency

- Double data rate (DDR) DRAM Relative to the externally supplied clock (SDRAM)

- Transfer on rising and falling clock edges

- Quad data rate (QDR) DRAM

- Separate DDR inputs and outputs

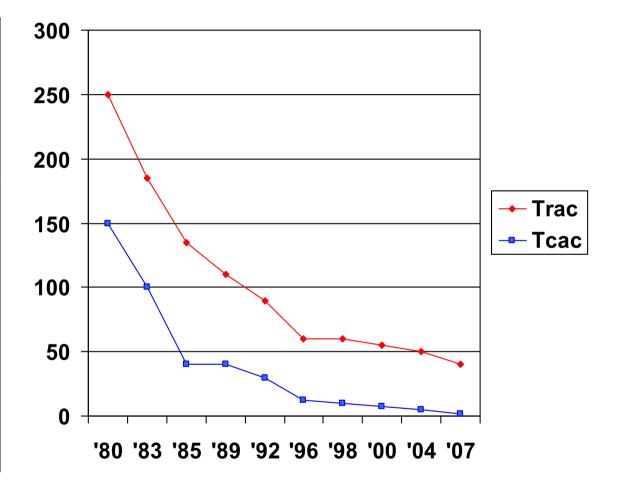

## **DRAM Generations**

| Year | Capacity | \$/GB     |

|------|----------|-----------|

| 1980 | 64Kbit   | \$1500000 |

| 1983 | 256Kbit  | \$500000  |

| 1985 | 1Mbit    | \$200000  |

| 1989 | 4Mbit    | \$50000   |

| 1992 | 16Mbit   | \$15000   |

| 1996 | 64Mbit   | \$10000   |

| 1998 | 128Mbit  | \$4000    |

| 2000 | 256Mbit  | \$1000    |

| 2004 | 512Mbit  | \$250     |

| 2007 | 1Gbit    | \$50      |

## **DRAM Performance Factors**

- Row buffer

- Allows several words to be read and refreshed in parallel

- Synchronous DRAM Operates in Synchrony with external clock

- **SDRAM**

- Allows for consecutive accesses in bursts without needing to send each address

- Improves bandwidth

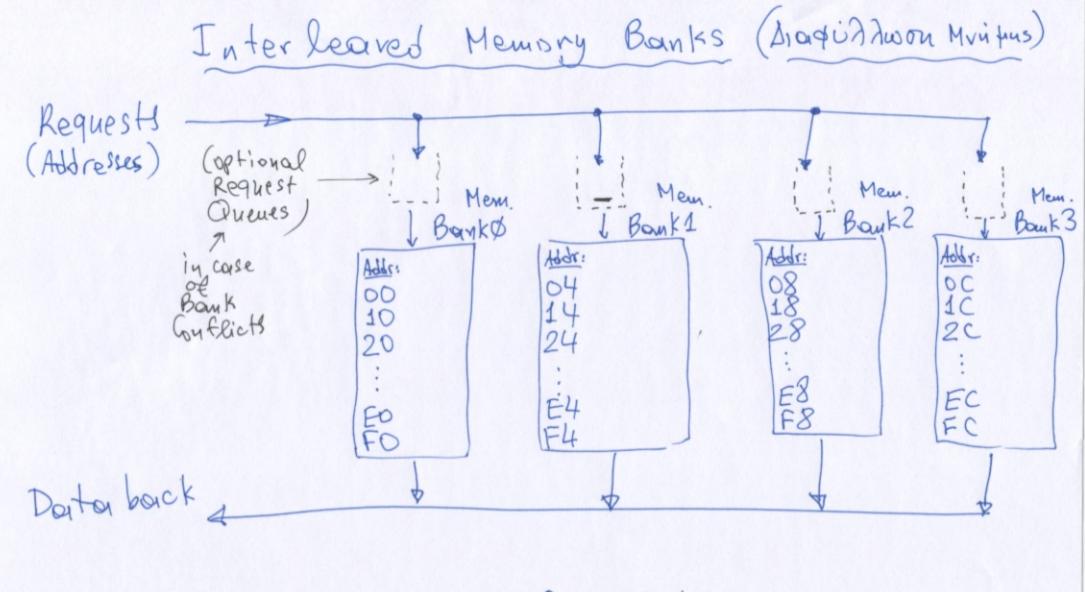

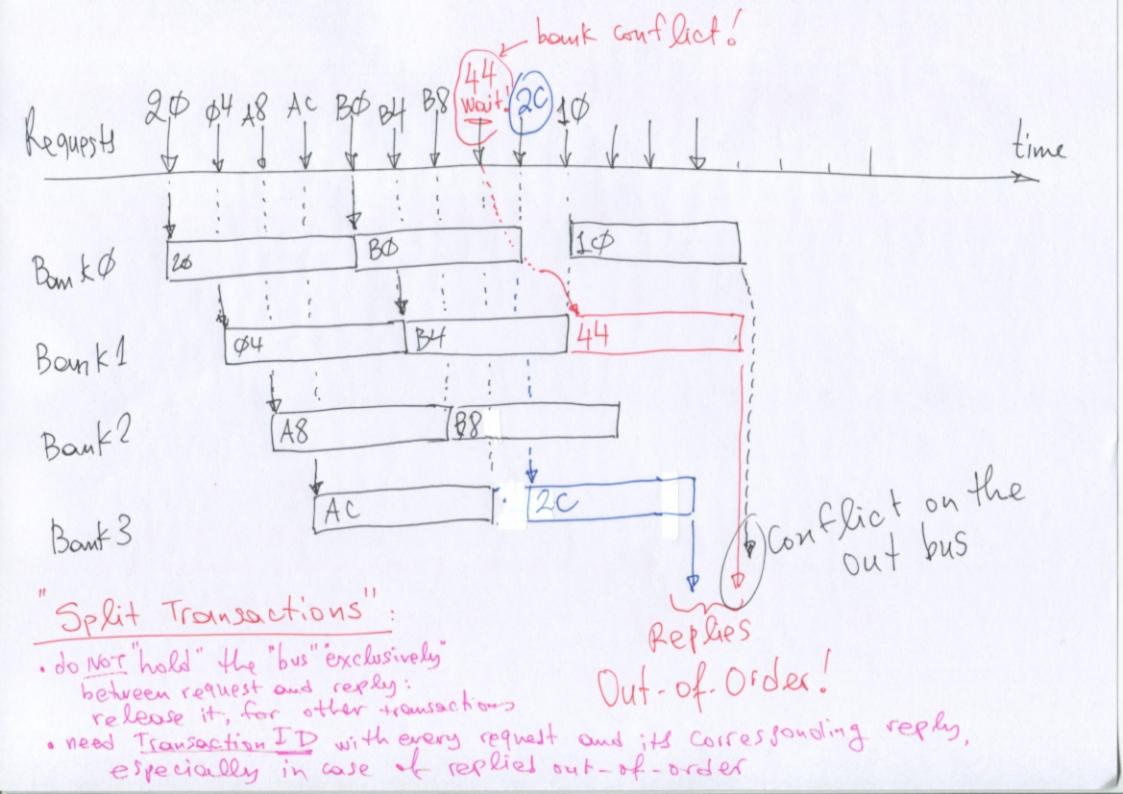

- DRAM banking (Interleaves Memory Banks)

- Allows simultaneous access to multiple DRAMs

- Improves bandwidth

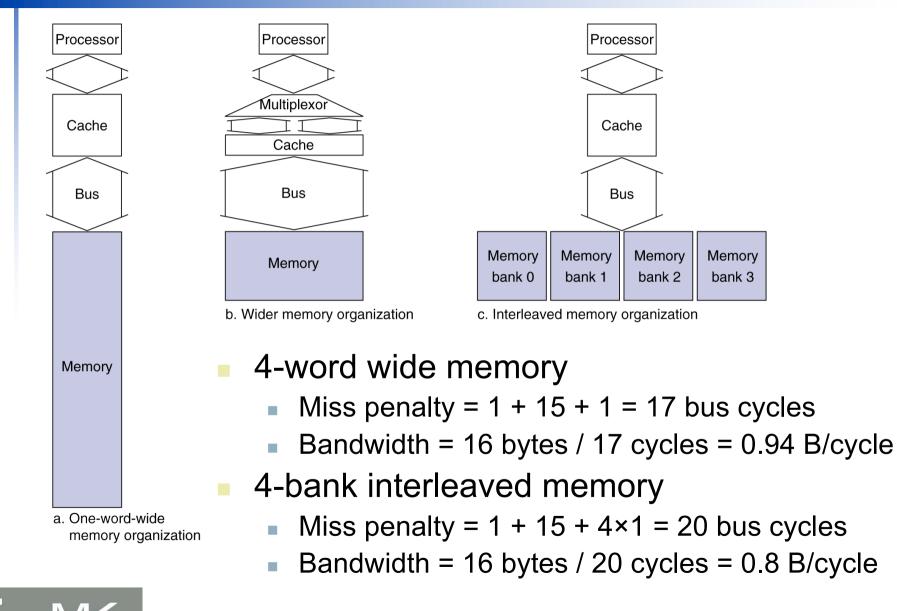

## **Increasing Memory Bandwidth**

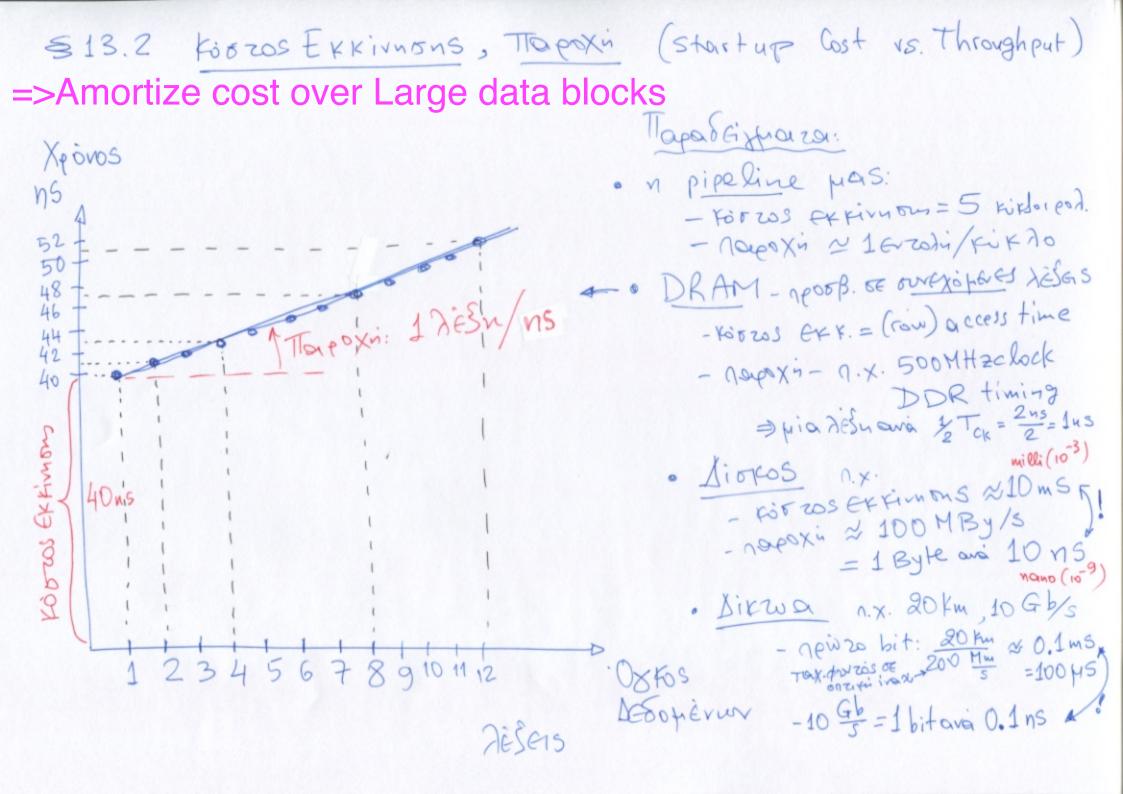

e.g.: 100 NS per Bounk Access, Request every 25 NS "Split Transactions" on request/reply "bus" ... pipelining ... multiple transactions interleaved in time

Chapter 6 — Storage and Other I/O Topics — 13

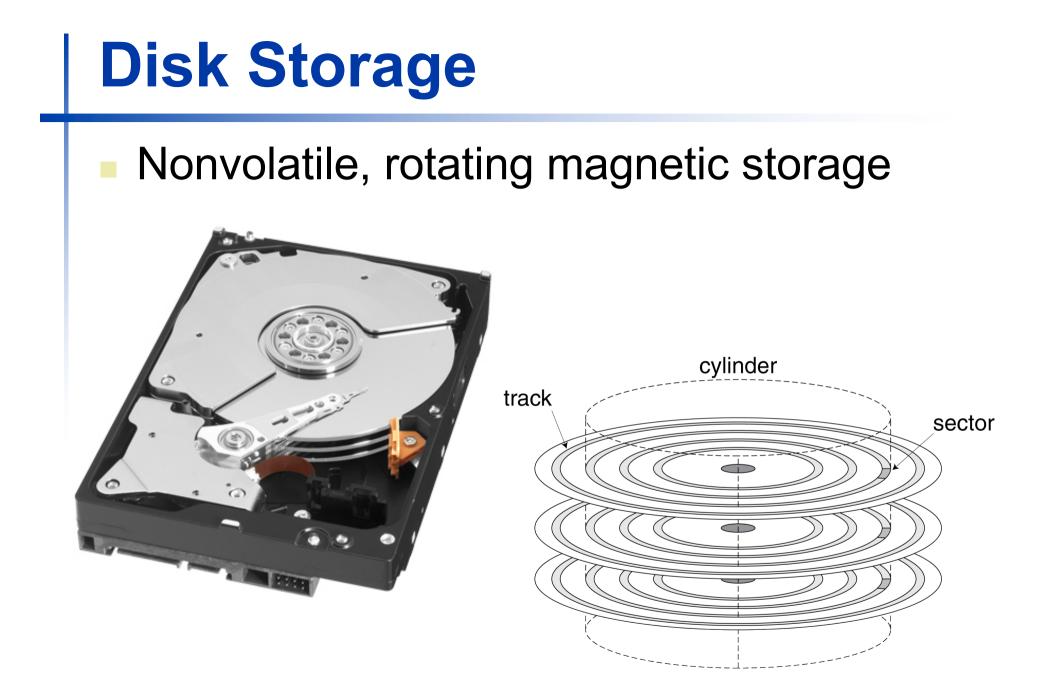

## **Disk Sectors and Access**

- Each sector records

- Sector ID

- Data (512 bytes, 4096 bytes proposed)

- Error correcting code (ECC)

- Used to hide defects and recording errors

- Synchronization fields and gaps

- Access to a sector involves

- Queuing delay if other accesses are pending

- Seek: move the heads

- Rotational latency

- Data transfer

- Controller overhead

# **Disk Access Example**

## Given

- 512B sector, 15,000rpm, 4ms average seek time, 100MB/s transfer rate, 0.2ms controller overhead, idle disk

- Average read time

- 4ms seek time

- $+ \frac{1}{2} / (15,000/60) = 2ms$  rotational latency

- + 512 / 100MB/s = 0.005ms transfer time

- + 0.2ms controller delay

- = 6.2ms

- If actual average seek time is 1ms

- Average read time = 3.2ms

# **Disk Performance Issues**

- Manufacturers quote average seek time

- Based on all possible seeks

- Locality and OS scheduling lead to smaller actual average seek times

- Smart disk controller allocate physical sectors on disk

- Present logical sector interface to host

- SCSI, ATA, SATA

- Disk drives include caches

- Prefetch sectors in anticipation of access

- Avoid seek and rotational delay

**Instruction Set Architecture for I/O**

- <sup>o</sup> Some machines have special input and output instructions

- <sup>o</sup> Alternative model (used by MIPS):

- Input: ~ reads a sequence of bytes

- Output: ~ writes a sequence of bytes

- <sup>o</sup> Memory also a sequence of bytes, so use loads for input, stores for output

- Called "<u>Memory Mapped Input/Output</u>"

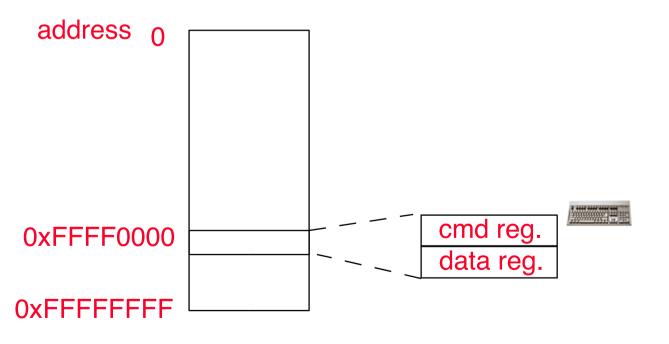

physical address space

7

A portion of the address space dedicated to communication paths to Input or Output devices (no memory there)

\*

# ° Certain addresses are not regular memory

#### Instead, they correspond to registers in I/O devices

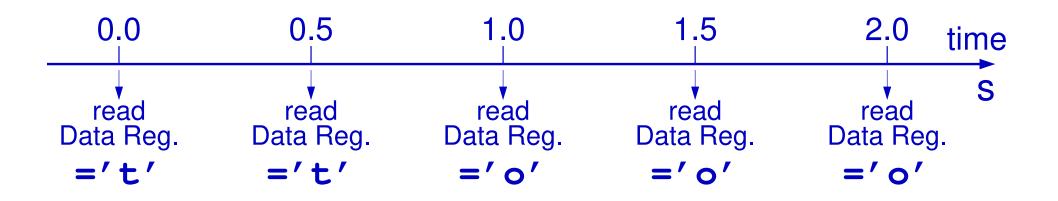

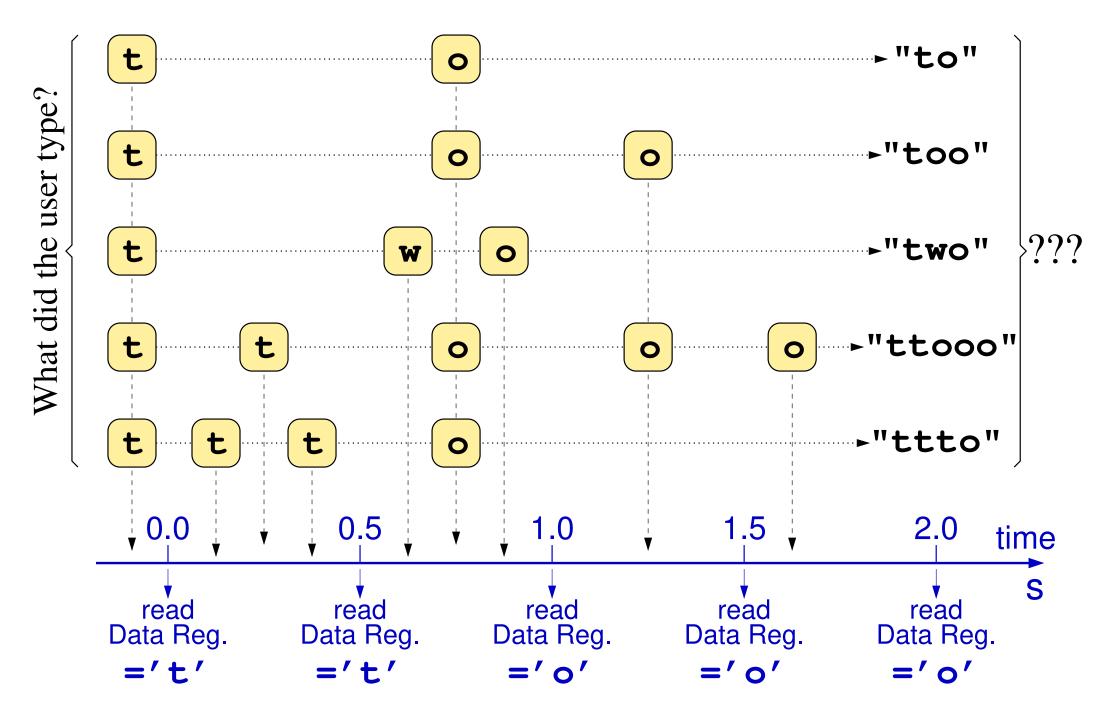

Example: keyboard... if only a Data Register:

### Example: keyboard... if only a Data Register:

**Processor Checks Status before Acting**

° Path to device generally has 2 registers:

- 1 register says it's OK to read/write (I/O ready), often called <u>Control Register</u>

- 1 register that contains data, often called <u>Data Register</u>

- <sup>o</sup> Processor reads from Control Register "Polling" in loop, waiting for device to set Ready bit in Control reg to say its OK (0 P 1) "Busy wait" if done

- Processor then loads from (input) or writes to (output) data register

\*

- "Busy wait" if done continuously; else, poll multiple devices on every interrupt from the real-time clock (usu. 50-120 Hz)

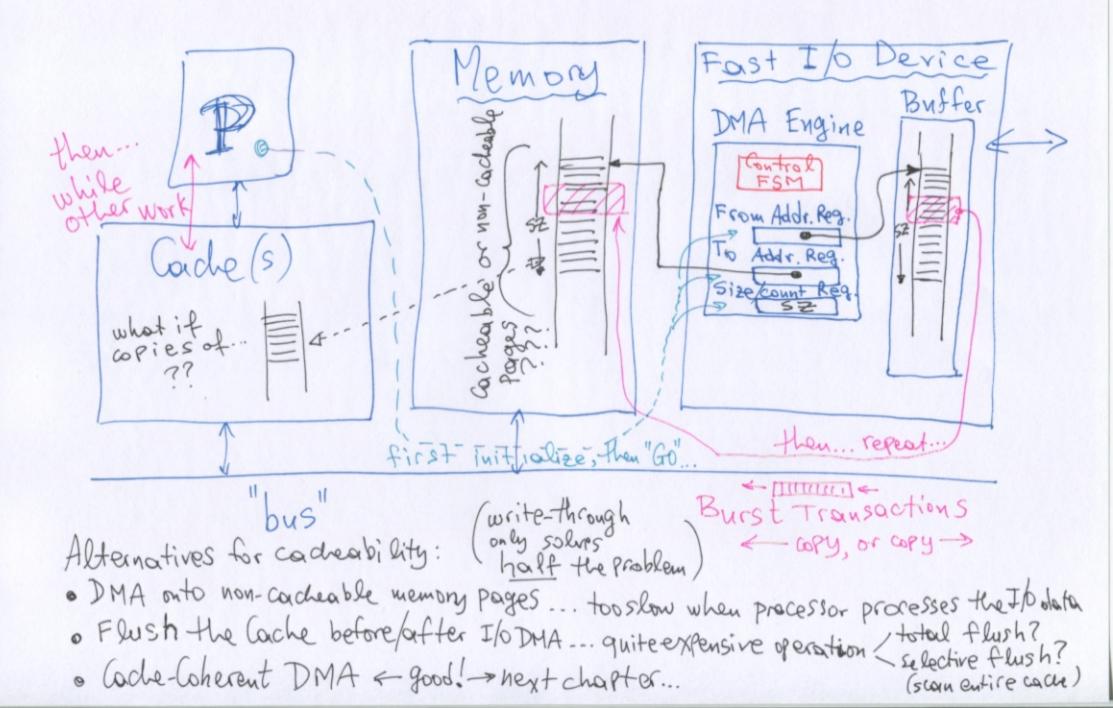

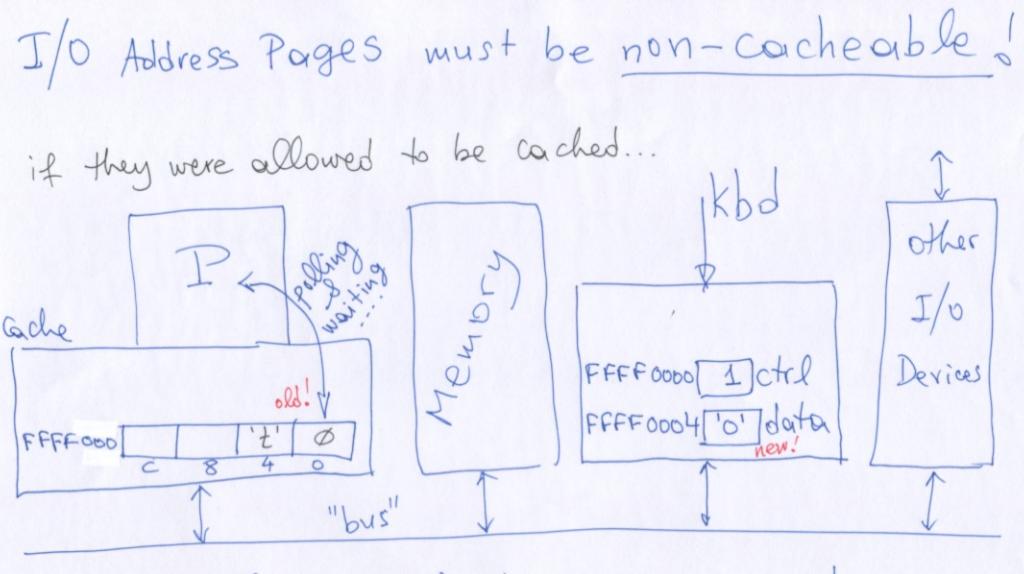

traditional ("non-coherent"...) caching does <u>NOT</u> work when other devices (I/0, other proc. cores) access memory independently

note: write-through is a "half-solution": works for output; but not for input...

Normal Memory Semantics (non-shared) I/O/Communication Registers 7 I/O/Communication Registers: Normal Memory: Solwewood: Some read ×1 Dotentially ≠ word: read ×2 Dotentially ≠ read ×3 Dotentially ≠ time Successive reads from a some location (without any inter reaging writes from processor) many yield different value! Kead glurays yeelds the last written value o write here > read/write here A may change other words too! data Not changed status writes only affect "Side-Effects" and the word being written

Memory Consistency (Ewénera Munifins) device or from from communic processor(s) write: from input reader: datal wait to see too showl?? -the flag data2 old be come 1 (i.en) data 3 then read do ready old ?? t laic inter Connection time hetwork time in-order or out-of-order eg. delivery? What if these reside on different memory bourks In our interleaved memory (

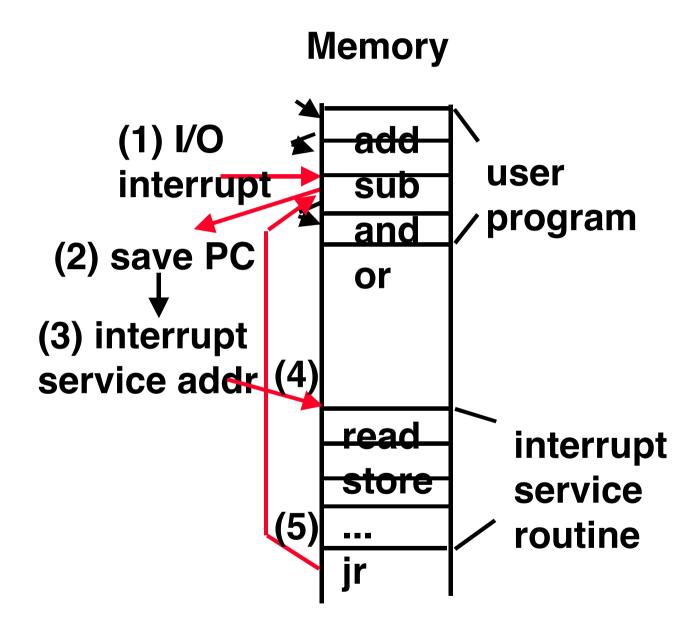

### What is the alternative to polling?

- <sup>o</sup> Wasteful to have processor spend most of its time "spin–waiting" for I/O to be ready

- <sup>o</sup> Wish we could have an unplanned procedure call that would be invoked only when I/O device is ready

- <sup>o</sup> Solution: use exception mechanism to help I/O. Interrupt program when I/O ready, return when done with data transfer

### An I/O interrupt is like an overflow exceptions except:

- An I/O interrupt is "asynchronous"

- More information needs to be conveyed

- ° An I/O interrupt is asynchronous with respect to instruction execution:

- I/O interrupt is not associated with any instruction, but it can happen in the middle of any given instruction

- I/O interrupt does not prevent any instruction from completion

## **Definitions for Clarification**

- <sup>o</sup> Exception: signal marking that something "out of the ordinary" has happened and needs to be handled

- Interrupt: asynchronous exception

- Trap: synchronous exception

- <sup>o</sup> Note: These are different from the book's definitions.

## **Interrupt Driven Data Transfer**

**Questions Raised about Interrupts**

- ° Which I/O device caused exception?

- Needs to convey the identity of the device generating the interrupt Cause register, or Vectored Interrupts

- °Can avoid interrupts during the interrupt routine?

- What if more important interrupt occurs while servicing this interrupt?

- Allow interrupt routine to be entered again?

- <sup>o</sup> Who keeps track of status of all the devices, handle errors, know where to put/supply the I/O data?

## Χρονικό κόστος Διακοπών και Δειγματοληψίας

- Παρ' ότι μιά εξαίρεση/διακοπή μοιάζει με άλμα, εντούτοις...

- Σχεδόν πάντα αυτά κοστίζουν ~1000 κύκλους ρολογιού (!)

- ένα μικρό μυστήριο το γιατί ακόμα ισχύει αυτό στη μεγάλη

πλειοψηφία, παρ' όλο που πολλοί προσπάθησαν να το μειώσουν

- μάλλον το άθροισμα κάμποσων παραγόντων, κυρίως:

- σώσιμο/επαναφορά καταχωρητών διακοπείσας διεργασίας

- αναζήτηση αιτίας / "housekeeping"

- αστοχίες κρυφών μνημών και TLB

- Δειγματοληψίες επίσης κοστίζουν: non-cacheable I/O reg.

- μία τεχνική: όταν διακοπή από real-time clock (~50-120 Hz), τότε το Λειτουργικό δειγματοληπτεί πολλές περιφερειακές μαζί

| Forst Devices need I/b                                                                                                                                                                                                                                                      | Buffer - not just a Register                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|

| Amortize the cost .                                                                                                                                                                                                                                                         | of Interrypt over many data                   |  |  |

| example:<br>(i at) 1 Ghit/s                                                                                                                                                                                                                                                 | I /o Buffer<br>e.g. [(fill one buffer by I/o, |  |  |

| (just) 1 Gbit/s                                                                                                                                                                                                                                                             | 4KBy e.g. by the processor)                   |  |  |

| TIOC                                                                                                                                                                                                                                                                        | D OF LEVEN                                    |  |  |

| 32 bits every 32ns (e.g. 1Gb/s)                                                                                                                                                                                                                                             | more 4 By every 32ns                          |  |  |

| "Register"<br>. Gost to poll startus register                                                                                                                                                                                                                               | 1 4 kBy every 5245                            |  |  |

| (non-cacheable, off-chip)<br>usually > DRAM access<br>usually ~ 100ns (or more)<br>usually ~ 100ns (or more) but this may still be a proceeding. OK                                                                                                                         |                                               |  |  |

| one<br>"Register"<br>• Gost to poll status register<br>(non-cacheenble, off-chip)<br>usually > DRAM access<br>usually ~ 100 ns (or more)<br>• then read the data register<br>similarly ~ 100 ns<br>• Cost of Interrupt + Kernel Interrupt handler waally ~ 1 yis (1000 ns). |                                               |  |  |

Direct Memory Access (DMA)