# Vivado Design Suite

George Matzouranis & Sotiris Totomis

CS-220

# FPGAs

- A field-programmable gate array (FPGA) is a circuit designed to be configured using hardware description language HDL

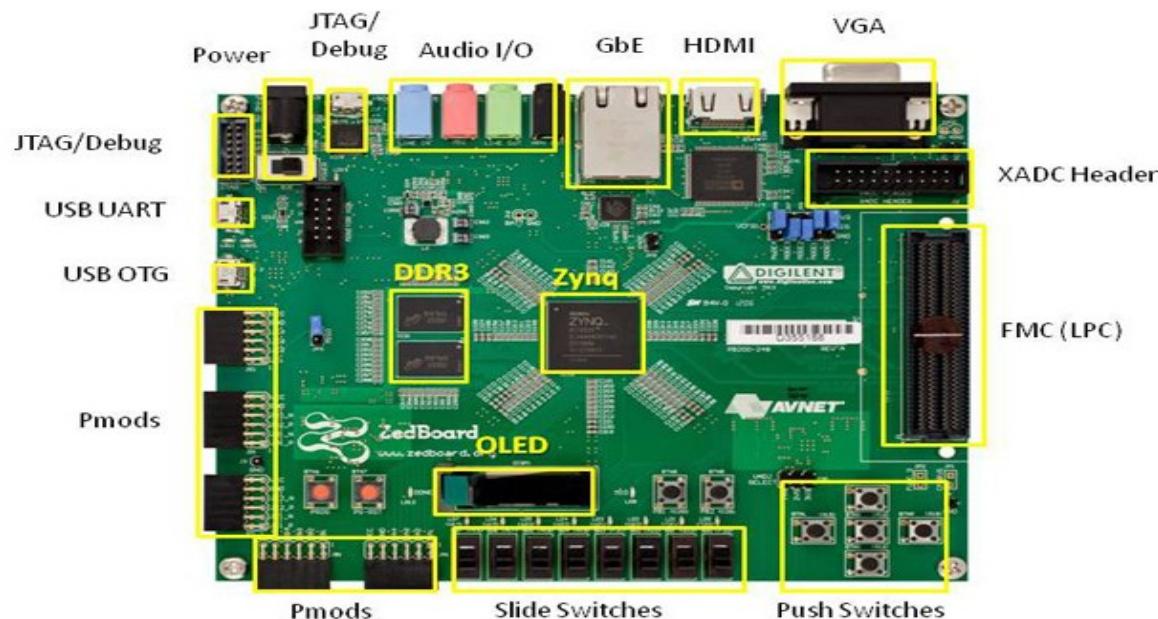

\* SD card cage and OSPI Flash reside on backside of board

# Vivado

Produced by Xilinx

- A software suite used for

- 1) Simulation

- 2) Synthesisof HDL (Hardware Design Language such as SystemVerilog) designs

# Simulation

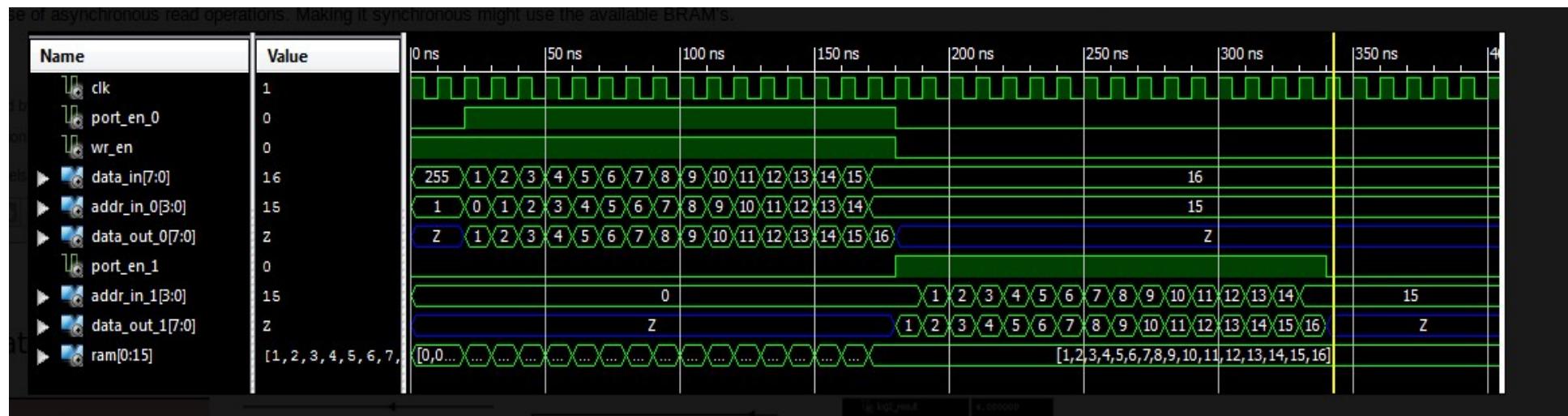

- The simulation of an electronic circuit helps the designer by visualizing the circuit's behavior

# Synthesis

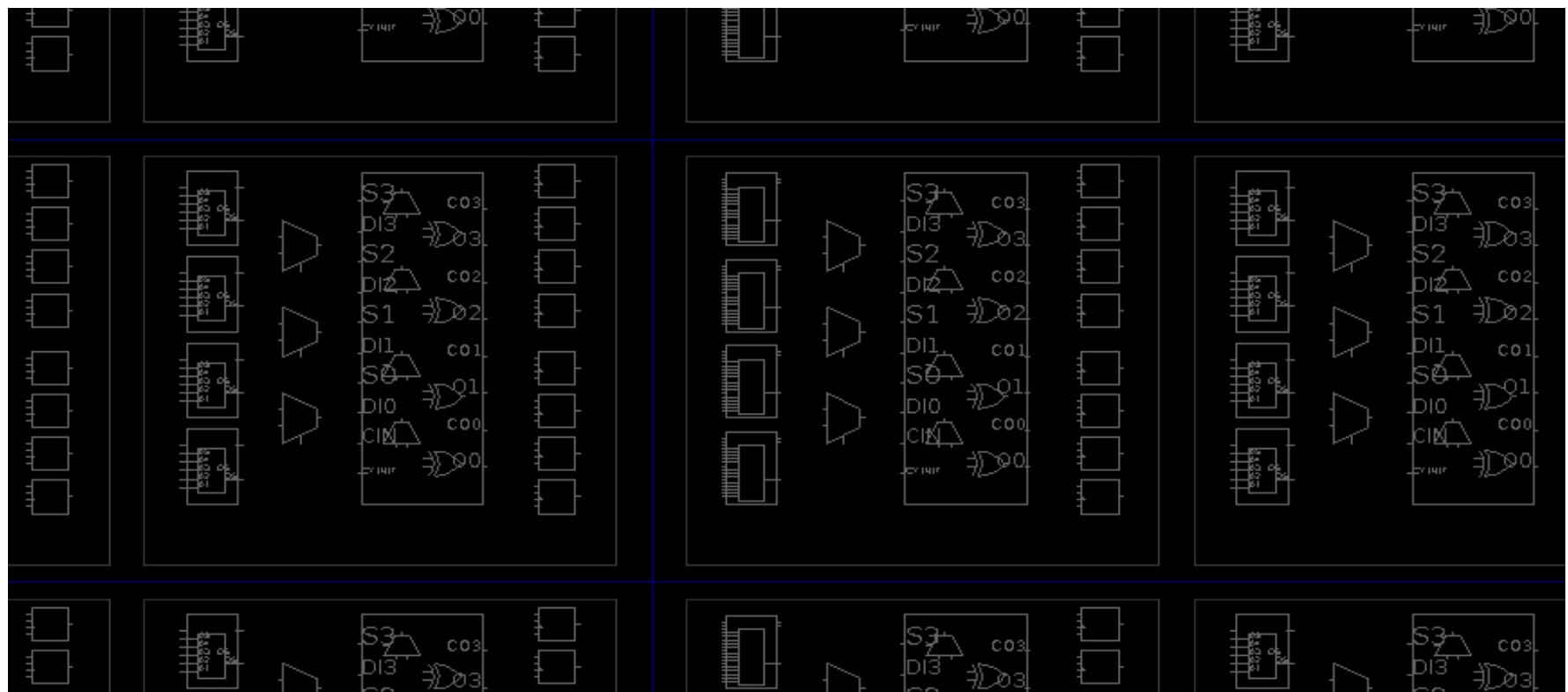

- Synthesis generates LUT-level schematic of the design

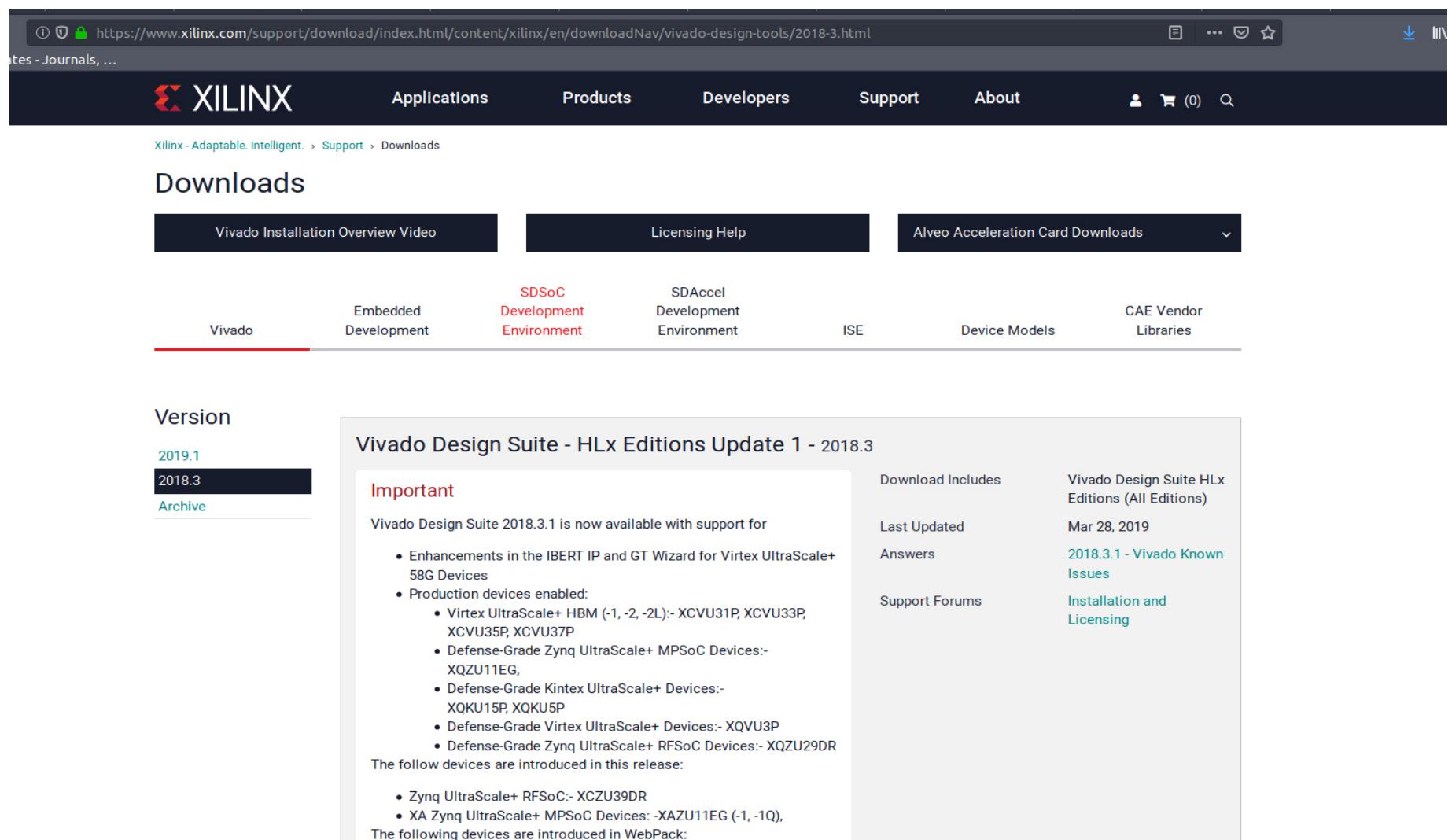

# Vivado Installation

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2018-3.html

XILINX Applications Products Developers Support About

Vivado - Journals, ...

Vivado Installation Overview Video Licensing Help Alveo Acceleration Card Downloads

Vivado Embedded Development SDSoC Development Environment SDAccel Development Environment ISE Device Models CAE Vendor Libraries

**Version**

2019.1

**2018.3**

Archive

**Vivado Design Suite - HLx Editions Update 1 - 2018.3**

**Important**

Vivado Design Suite 2018.3.1 is now available with support for

- Enhancements in the IBERT IP and GT Wizard for Virtex UltraScale+ 58G Devices

- Production devices enabled:

- Virtex UltraScale+ HBM (-1, -2, -2L):- XCVU31P, XCVU33P, XCVU35P, XCVU37P

- Defense-Grade Zynq UltraScale+ MPSoC Devices:- XQZU11EG,

- Defense-Grade Kintex UltraScale+ Devices:- XQKU15P, XQKU5P

- Defense-Grade Virtex UltraScale+ Devices:- XQVU3P

- Defense-Grade Zynq UltraScale+ RFSoC Devices:- XQZU29DR

The following devices are introduced in this release:

- Zynq UltraScale+ RFSoC:- XCZU39DR

- XA Zynq UltraScale+ MPSoC Devices: -XAZU11EG (-1, -1Q),

The following devices are introduced in WebPack:

Download Includes Vivado Design Suite HLx Editions (All Editions)

Last Updated Mar 28, 2019

Answers 2018.3.1 - Vivado Known Issues

Support Forums Installation and Licensing

# Vivado Installation (cont'd)

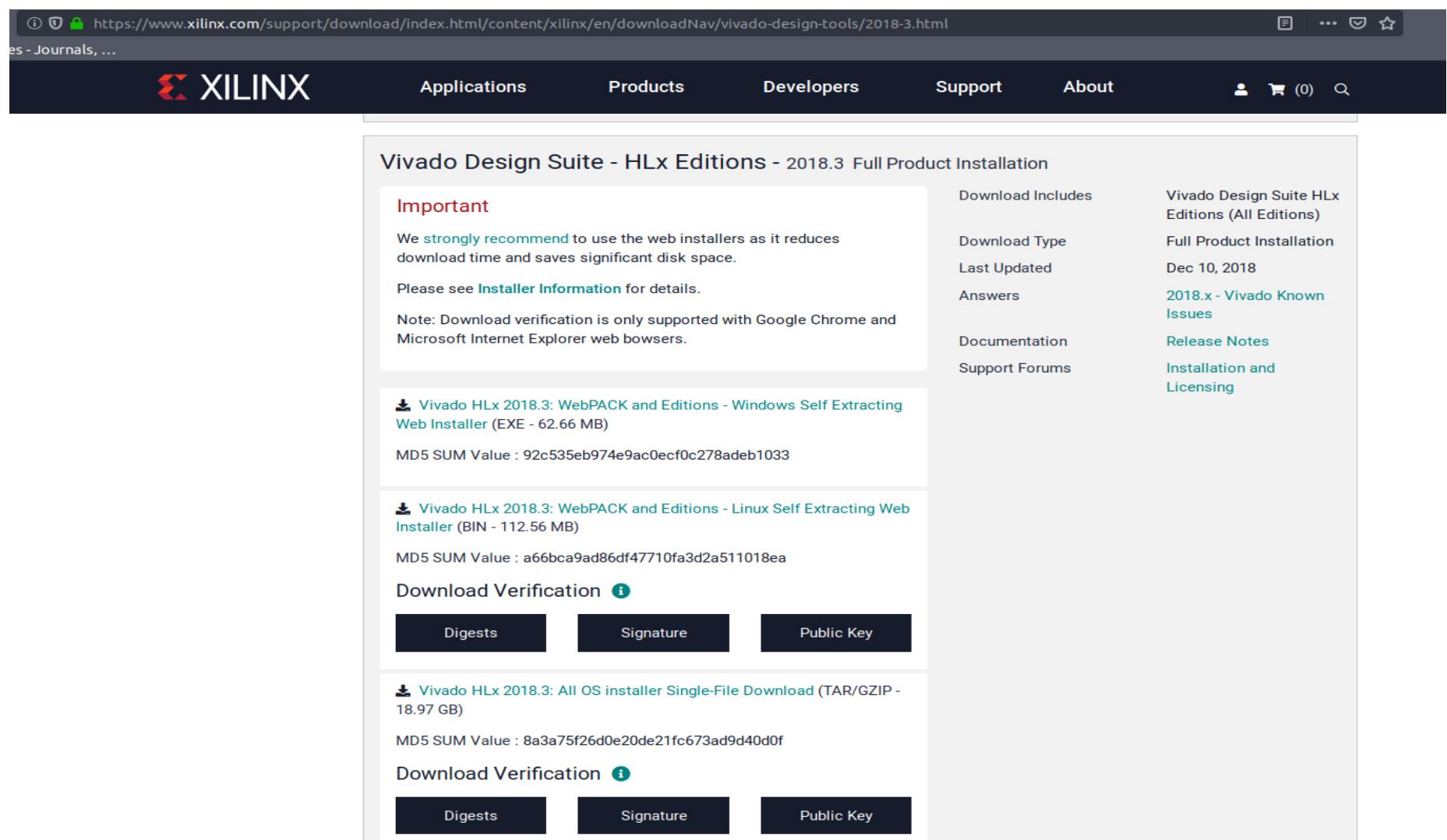

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2018-3.html

**Vivado Design Suite - HLx Editions - 2018.3 Full Product Installation**

**Important**

We **strongly recommend** to use the web installers as it reduces download time and saves significant disk space.

Please see [Installer Information](#) for details.

Note: Download verification is only supported with Google Chrome and Microsoft Internet Explorer web browsers.

**Download Includes**

Vivado Design Suite HLx Editions (All Editions)

**Download Type**

Full Product Installation

**Last Updated**

Dec 10, 2018

**Answers**

[2018.x - Vivado Known Issues](#)

**Documentation**

[Release Notes](#)

**Support Forums**

[Installation and Licensing](#)

**Download Links**

[Vivado HLx 2018.3: WebPACK and Editions - Windows Self Extracting Web Installer \(EXE - 62.66 MB\)](#)

MD5 SUM Value : 92c535eb974e9ac0ecf0c278adeb1033

[Vivado HLx 2018.3: WebPACK and Editions - Linux Self Extracting Web Installer \(BIN - 112.56 MB\)](#)

MD5 SUM Value : a66bca9ad86df47710fa3d2a511018ea

**Download Verification** ⓘ

[Digests](#) [Signature](#) [Public Key](#)

[Vivado HLx 2018.3: All OS installer Single-File Download \(TAR/GZIP - 18.97 GB\)](#)

MD5 SUM Value : 8a3a75f26d0e20de21fc673ad9d40d0f

**Download Verification** ⓘ

[Digests](#) [Signature](#) [Public Key](#)

# Vivado Installation (cont'd)

Vivado 2018.3 Installer - Welcome

**Welcome**

We are glad you've chosen Xilinx as your platform development partner. This program can install the Vivado Design Environment, Software Development Kit and Documentation Navigator.

Supported operating systems for Vivado 2018.3 are:

- Windows 7.1: 64-bit

- Windows 10 Professional versions 1803 and 1809: 64-bit

- Red Hat Enterprise Linux 6.6-6.9: 64-bit

- Red Hat Enterprise Linux 7.2-7.5: 64-bit

- CentOS Linux 6.6-6.9: 64-bit

- CentOS Linux 7.2-7.5: 64-bit

- SUSE Enterprise Linux 11.4: 64-bit

- SUSE Enterprise Linux 12.3: 64-bit

- Ubuntu Linux 16.04.4 and 18.04 LTS: 64-bit - Additional library installation required

Note: This release requires upgrading your license server tools to the Flex 11.14.1 versions. Please confirm with your license admin that the correct version of the license server tools are installed and available, before running the tools.

Note: This installation program will not install cable drivers on Linux. This item will need to be installed separately, with administrative privileges.

To reduce installation time, we recommend that you disable any anti-virus software before continuing.

**XILINX**

Copyright © 1986-2019 Xilinx, Inc. All rights reserved.

Preferences < Back Next > Cancel

# Vivado Installation (cont'd)

**Vivado 2018.3 Installer - Select Install Type**

**Select Install Type**

Please select install type and provide your Xilinx.com user ID and password for authentication.

**User Authentication**

Please provide your Xilinx user account credentials to download the required files.

If you don't have an account, [please create one](#). If you forgot your password, you can [reset it here](#).

User ID

Password

Download and Install Now

Select your desired device and tool installation options and the installer will download and install just what is required. Downloaded installation files will be saved for future use. NOTE: Future installs using these downloaded files will be restricted to the options selected during this install. For access to all options later, choose "Download Full Image".

Download Full Image (Install Separately)

The installer will download an image containing all devices and tool options for later installation. Use this option if you wish to install a full image on a network drive or allow different users maximum flexibility when installing.

Copyright © 1986-2019 Xilinx, Inc. All rights reserved.

[< Back](#) [Next >](#) [Cancel](#)

# Vivado Installation (cont'd)

**Vivado 2018.3 Installer - Accept License Agreements**

**Accept License Agreements**

Please read the following terms and conditions and indicate that you agree by checking the I Agree checkboxes.

**Xilinx Inc. End User License Agreement**

By checking "I AGREE" below, or OTHERWISE ACCESSING, DOWNLOADING, INSTALLING or USING THE SOFTWARE, YOU AGREE on behalf of licensee to be bound by the agreement, which can be viewed by [clicking here](#).

I Agree

**WebTalk Terms And Conditions**

By checking "I AGREE" below, I also confirm that I have read [Section 13 of the terms and conditions](#) above concerning WebTalk and have been afforded the opportunity to read the WebTalk FAQ posted at <https://www.xilinx.com/products/design-tools/webtalk.html>. I understand that I am able to disable WebTalk later if certain criteria described in Section 13(c) apply. If they don't apply, I can disable WebTalk by uninstalling the Software or using the Software on a machine not connected to the internet. If I fail to satisfy the applicable criteria or if I fail to take the applicable steps to prevent such transmission of information, I agree to allow Xilinx to collect the information described in Section 13(a) for the purposes described in Section 13(b).

I Agree

**Third Party Software End User License Agreement**

By checking "I AGREE" below, or OTHERWISE ACCESSING, DOWNLOADING, INSTALLING or USING THE SOFTWARE, YOU AGREE on behalf of licensee to be bound by the agreement, which can be viewed by [clicking here](#).

I Agree

Copyright © 1986-2019 Xilinx, Inc. All rights reserved.

[< Back](#) [Next >](#) [Cancel](#)

# Vivado Installation (cont'd)

**Vivado 2018.3 Installer - Select Edition to Install**

**Select Edition to Install**

Select an edition to continue installation. You will be able to customize the content in the next page.

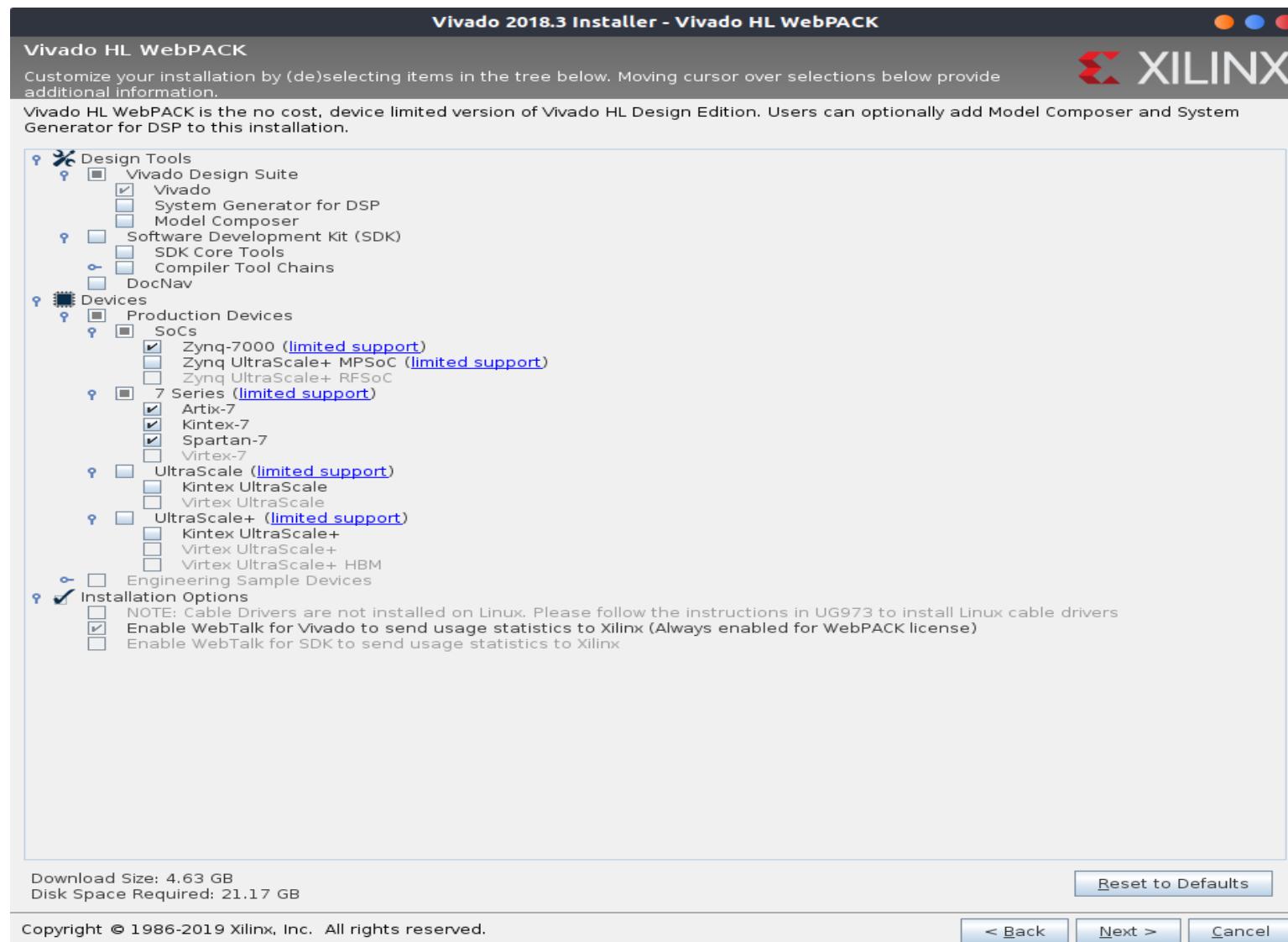

**Vivado HL WebPACK**

Vivado HL WebPACK is the no cost, device limited version of Vivado HL Design Edition. Users can optionally add Model Composer and System Generator for DSP to this installation.

**Vivado HL Design Edition**

Vivado HL Design Edition includes the full complement of Vivado Design Suite tools for design, including C-based design with Vivado High-Level Synthesis, implementation, verification and device programming. Complete device support, cable drivers and Documentation Navigator are included. Users can optionally add Model Composer to this installation.

**Vivado HL System Edition**

Vivado HL System Edition is a superset of Vivado HL Design Edition with the addition of System Generator for DSP. Complete device support, cable drivers and Documentation Navigator are included. Users can optionally add Model Composer to this installation.

**Documentation Navigator (Standalone)**

Xilinx Documentation Navigator (DocNav) provides access to Xilinx technical documentation both on the Web and on the Desktop. This is a standalone installation without Vivado Design Suite.

Copyright © 1986-2019 Xilinx, Inc. All rights reserved.

[< Back](#) [Next >](#) [Cancel](#)

# Vivado Installation (cont'd)

# Vivado Installation (cont'd)

# Vivado Installation (cont'd)

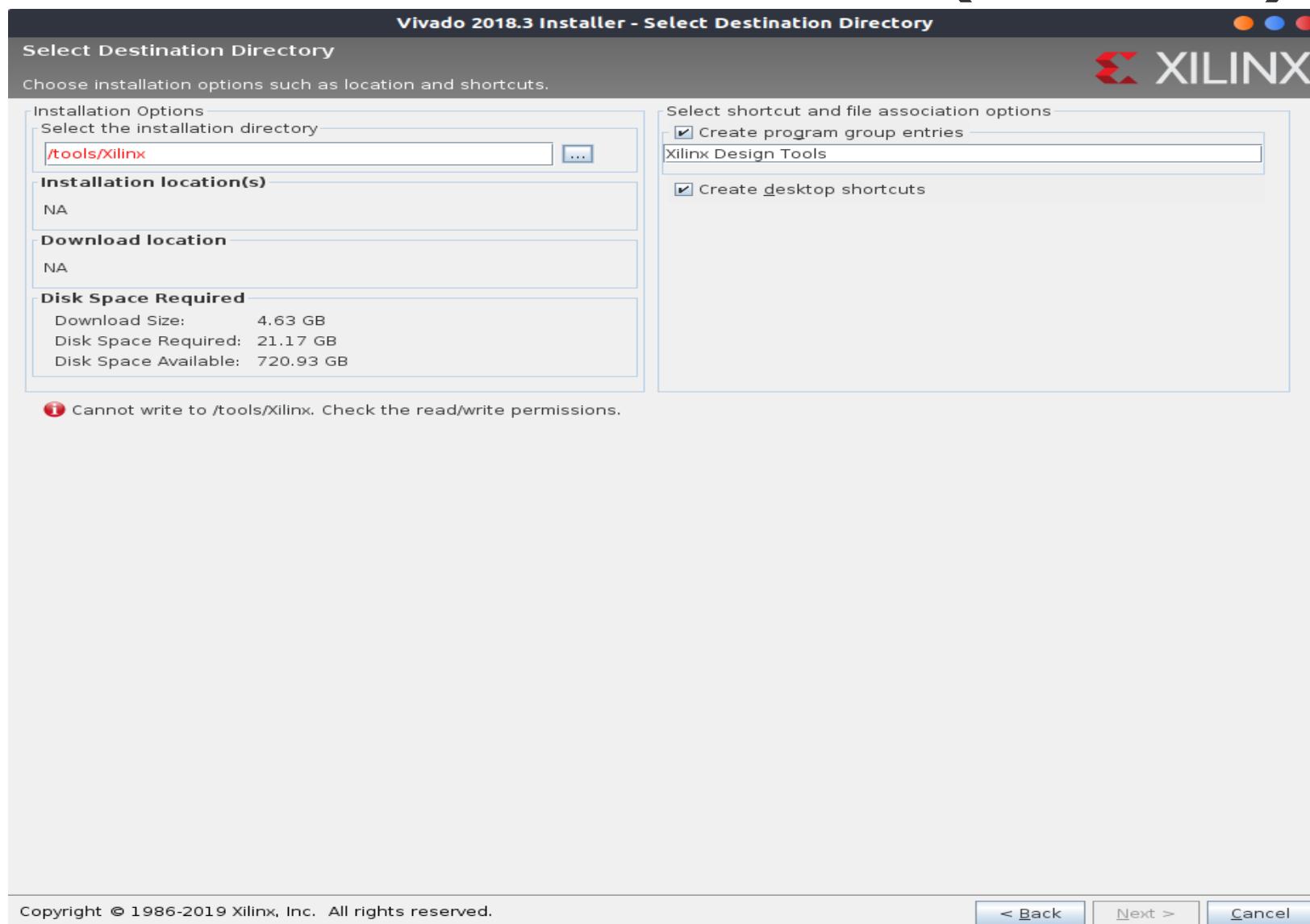

Vivado 2018.3 Installer - Installation Summary

**Installation Summary**

**Edition: Vivado HL WebPACK**

**Devices**

- Production Devices (SoCs, 7 Series)

**Design Tools**

- Vivado Design Suite (Vivado)

**Installation Options**

- Enable WebTalk for Vivado to send usage statistics to Xilinx (Always enabled for WebPACK license)

**Installation location**

- /home/sototo/Vivado/2018.3

**Download location**

- /home/sototo/Downloads/Vivado\_2018.3

**Disk Space Required**

- Download Size: 4.63 GB

- Disk Space Required: 21.17 GB

**XILINX**

Copyright © 1986-2019 Xilinx, Inc. All rights reserved.

Preferences < Back Install Cancel

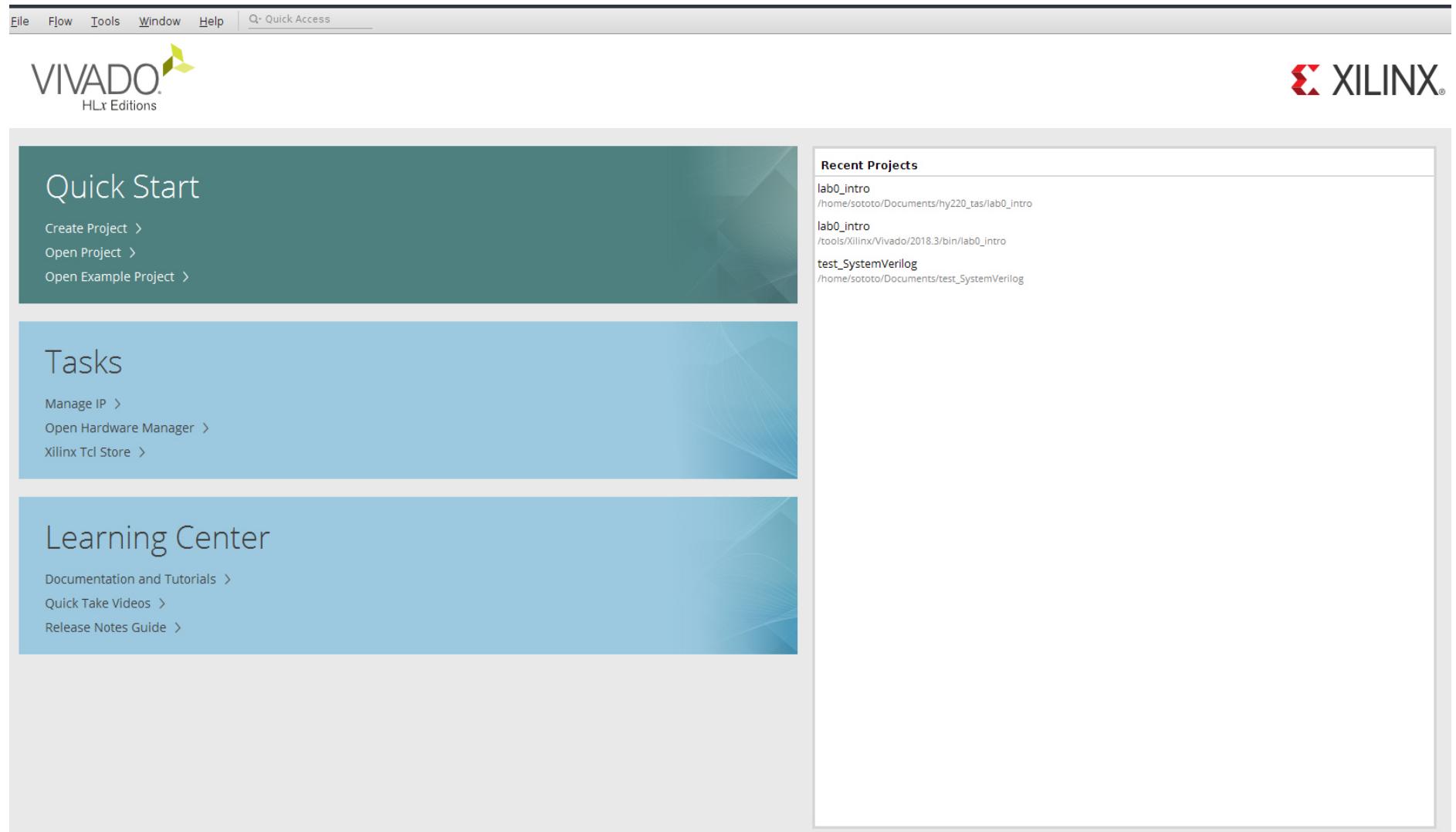

# Creating a project

The screenshot shows the Vivado HLx Editions software interface. The top navigation bar includes 'File', 'Flow', 'Tools', 'Window', 'Help', and a 'Quick Access' search bar. The Vivado logo and 'HLx Editions' text are in the top left. The Xilinx logo is in the top right. The interface is divided into several sections:

- Quick Start:** Contains links to 'Create Project', 'Open Project', and 'Open Example Project'.

- Tasks:** Contains links to 'Manage IP', 'Open Hardware Manager', and 'Xilinx Tcl Store'.

- Learning Center:** Contains links to 'Documentation and Tutorials', 'Quick Take Videos', and 'Release Notes Guide'.

- Recent Projects:** A sidebar listing recent projects with their paths:

- lab0\_intro /home/sototo/Documents/hy220\_tas/lab0\_intro

- lab0\_intro /tools/Xilinx/Vivado/2018.3/bin/lab0\_intro

- test\_SystemVerilog /home/sototo/Documents/test\_SystemVerilog

# Creating a project (cont'd)

# Creating a project (cont'd)

New Project

**Project Type**

Specify the type of project to create.

- RTL Project**

You will be able to add sources, create block designs in IP Integrator, generate IP, run RTL analysis, synthesis, implementation, design planning and analysis.

Do not specify sources at this time

- Post-synthesis Project:** You will be able to add sources, view device resources, run design analysis, planning and implementation.

Do not specify sources at this time

- I/O Planning Project**

Do not specify design sources. You will be able to view part/package resources.

- Imported Project**

Create a Vivado project from a Synplify, XST or ISE Project File.

- Example Project**

Create a new Vivado project from a predefined template.

[? < Back](#) [Next >](#) [Finish](#) [Cancel](#)

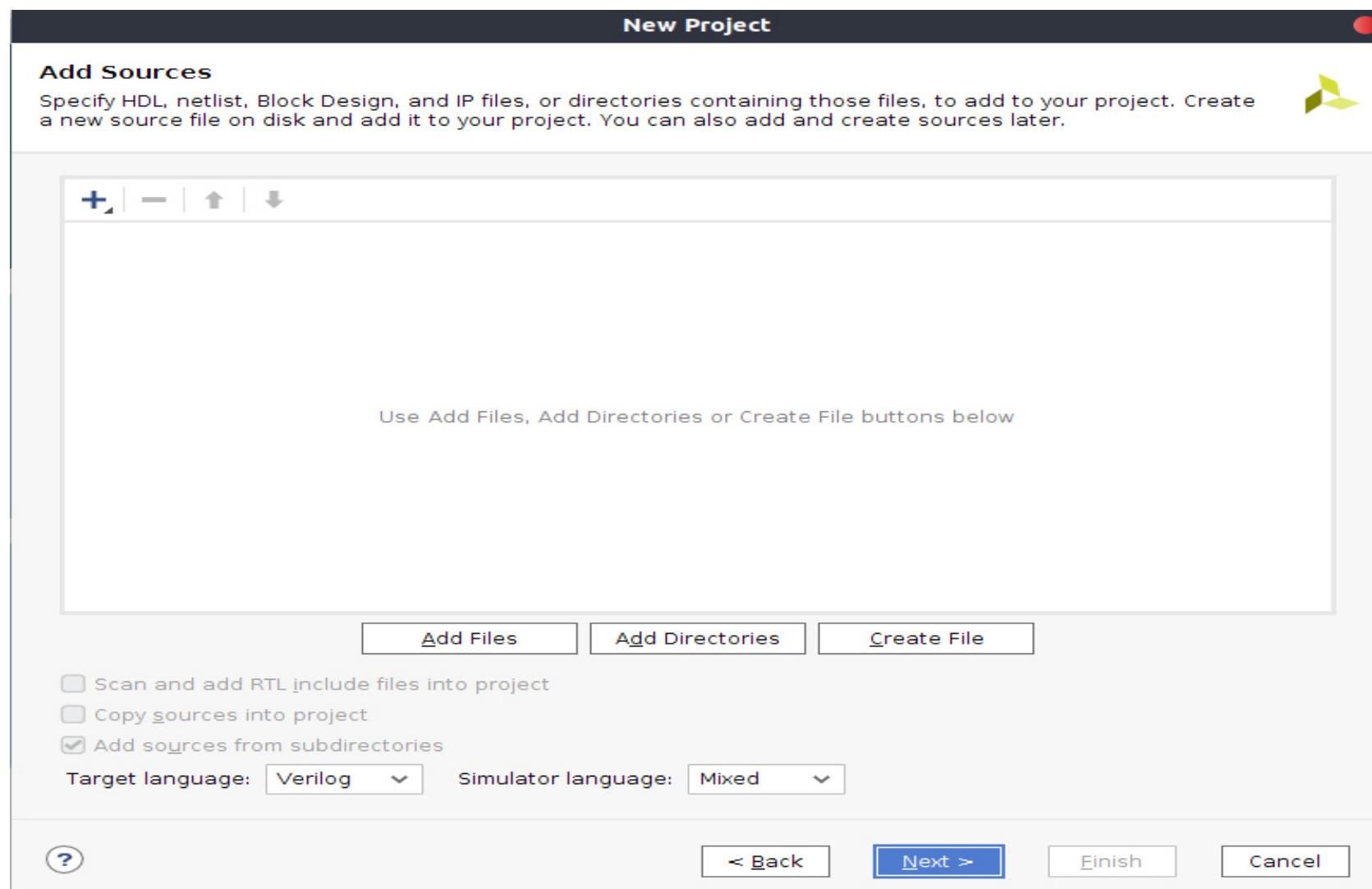

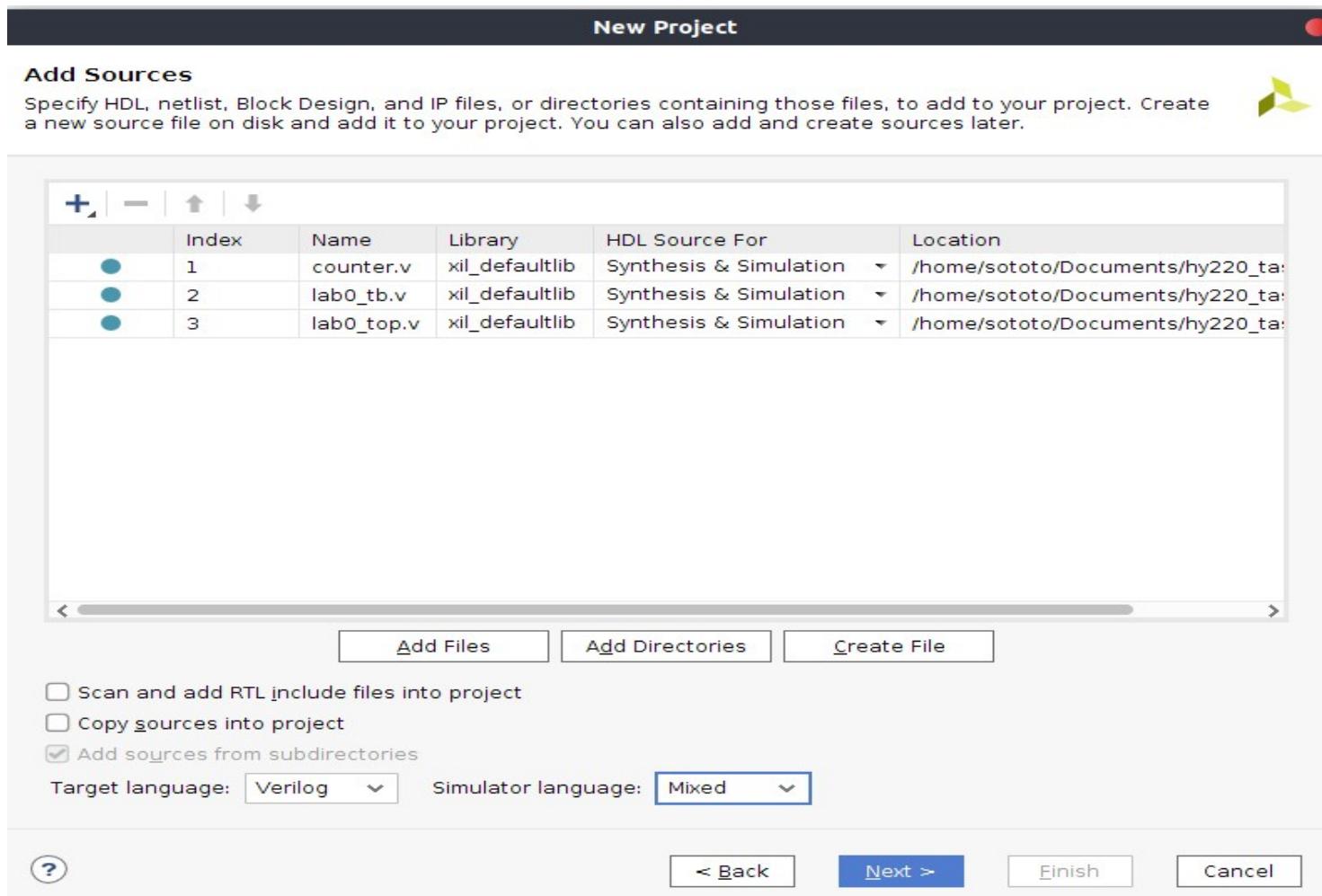

# Creating a project (cont'd)

# Create a project (cont'd)

- Wrong!!!

- lab0\_tb.v must be set for simulation only!!!

- Testbenches include non-synthesizable code!!!

# Create a project (cont'd)

New Project

Add Constraints (optional)

Specify or create constraint files for physical and timing constraints.

**+** | **-** | **↑** | **↓**

Use Add Files or Create File buttons below

**Add Files** **Create File**

Copy constraints files into project

**?** **< Back** **Next >** **Finish** **Cancel**

# Constraints file

- When programming an FPGA through software such as Xilinx's Vivado, you need to inform the software what physical pins on the FPGA that you plan on using.

- Xilinx Design Constraints file (XDC file)

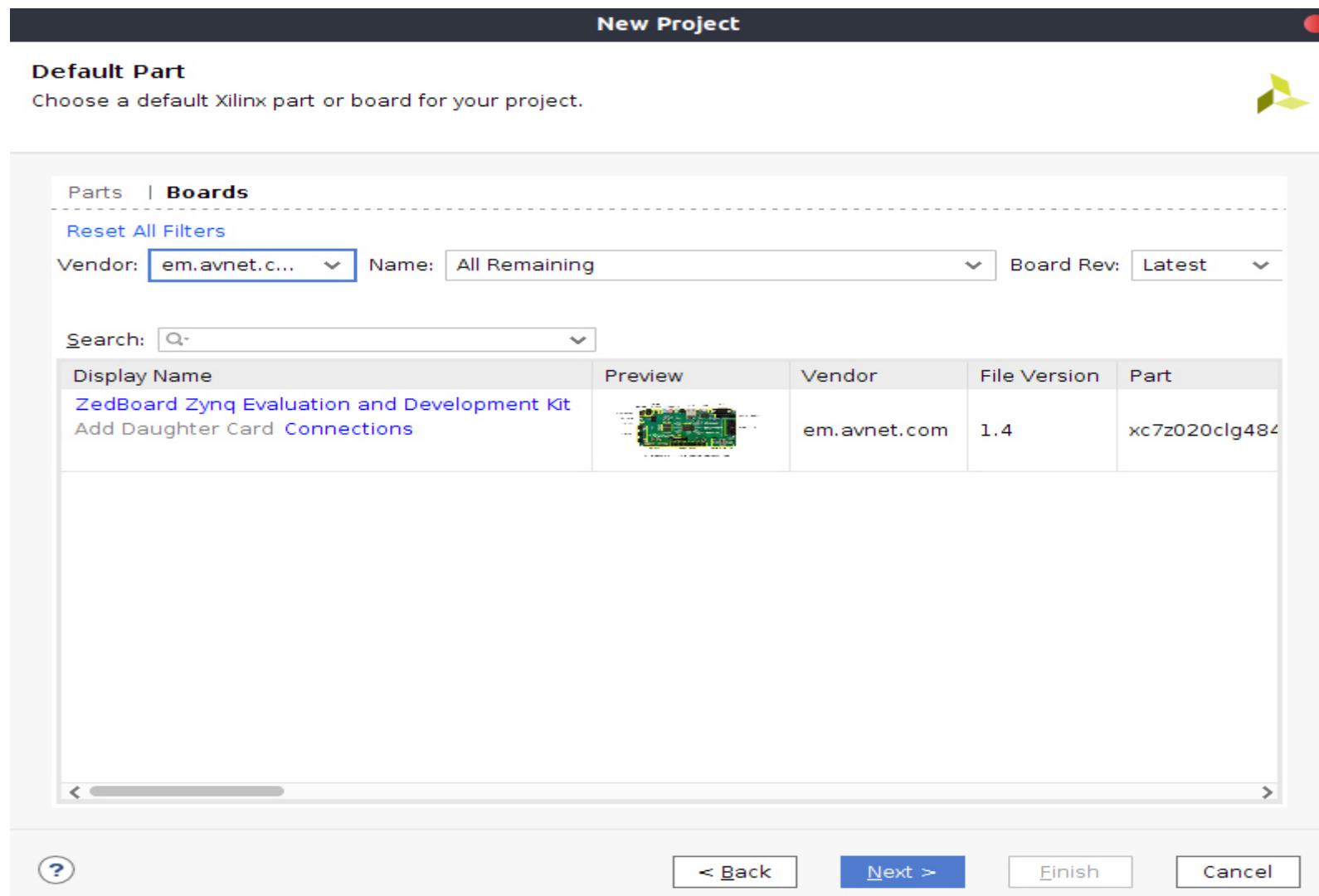

# Creating a project (cont'd)

# Flow Navigator

- Run Simulation

- Will show the waveform of the design that represents its behavior

- most bugs can be caught here!!!

- Open Elaborated Design

- Generates the schematic of your code

- can be useful when you want to know exactly all and non-trivial connections of the design

# Flow Navigator

- Run Synthesis

- Will show the corresponding LUT schematic of the selected device

- Info about timing, utilization and critical paths!!!

- Run Implementation

- Here the same schematic as before will be showed with the design implemented on it for our selected device

# Flow Navigator

- Generate Bitstream

- In here the bitstream is generated by the initial design in order to program the selected device

- Open Hardware Manager

- Open Target to find the connected device

- Program Device to download the generated bitstream to the connected device!

# Demo time!!!

Questions...?