| ΗΥ-120: Ψηφιακή Σχεδίαση

Φθινόπωρο 2020 |

Τμ. Επ. Υπολογιστών © Πανεπιστήμιο Κρήτης |

Εργαστήριο 3:

Πολυπλέκτες - Αποκωδικοποιητές, Ανάδραση - Ταλάντωση - Μνήμη,

Πύλες, Transistors, Chips, Συνδυαστικά Κυκλώματα

26 - 31 Οκτωβρίου 2020 (βδομάδα 6)

|

[Up - Table of Contents] [Prev - 2. Relays] |

[4. Karnaugh, RAM - Next] |

[Βιβλία: προαιρετικά μπορείτε να διαβάσετε τις σελίδες: Dally: §4.1 και §4.3.1-2 (και γιά μελέτη πέραν της ύλης του μαθήματος: §4.2, 4.3.3)· Mano: (5η έκδοση) σελ. 60-69 (§2.8-2.9)· Wakerly: (3η έκδοση) σελ. 93-117 (§3.1-3.4) (και γιά μελέτη πέραν της ύλης του μαθήματος: §3.5 (σελ. 117-134))].

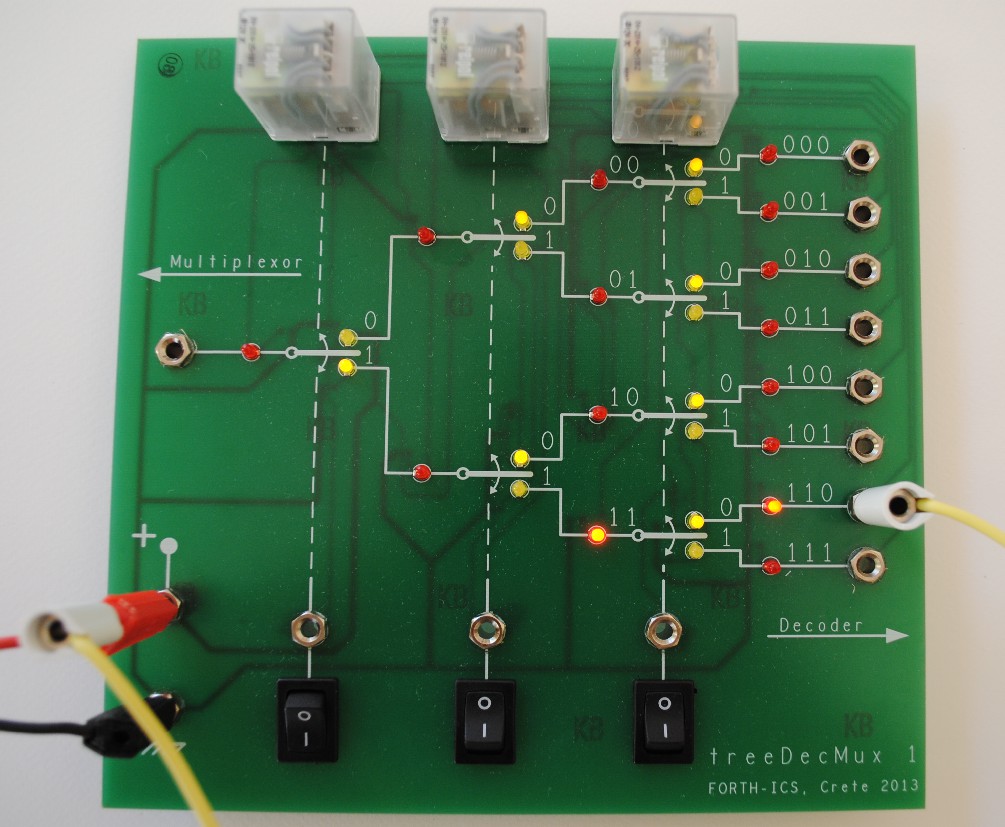

Πείραμα 3.1: Κωδικοποιημένα Σήματα Επιλογής: Πολυπλέκτης με Αποκωδικοποιητή

Στην §1.5 μιλήσαμε γιά τους πολυπλέκτες. Εκεί, η επιλογή της επιθυμητής εισόδου δεδομένων γίνονταν μέσω ενός διακόπτη ανά είσοδο, και έπρεπε ένας και μόνον ένας από αυτούς τους διακόπτες επιλογής να είναι ενεργοποιημένος (πατημένος - επιλεγμένος) κάθε στιγμή. Στο σχήμα εδώ δεξιά φαίνεται ένας τέτοιος πολυπλέκτης 8-σε-1: έχει 8 εισόδους δεδομένων, Data0 έως Data7, 8 διακόπτες επιλογής (select), S0 έως S7, και μία έξοδο δεδομένων, DataOut, η οποία ισούται ανά πάσα στιγμή με εκείνην από τις εισόδους δεδομένων η οποία αντιστοιχεί στον (μοναδικό!) διακόπτη επιλογής που είναι πατημένος εκείνη τη στιγμή.Άλλες φορές, όμως, την επιλογή εισόδου προτιμάμε να την κάνουμε με διαφορετικό τρόπο: χρησιμοποιούμε λιγότερους διακόπτες επιλογής (λιγότερες εισόδους επιλογής), και αποκωδικοποιούμε αυτές τις λιγότερες εισόδους στους (πολύ περισσότερους) συνδυασμούς που αυτές παράγουν, και ο κάθε ένας από αυτούς τους συνδυασμούς επιλέγει μιάν αντίστοιχη είσοδο δεδομένων. Με τον τρόπο αυτό υπάρχει διπλό κέρδος: (i) χρειαζόμαστε πολύ λιγότερες εισόδους επιλογής (ελέγχου), και (ii) το κύκλωμα αποκωδικοποίησης μας εξασφαλίζει αυτό που είχαμε (άτυπα) συμφωνήσει ότι θέλουμε: κάθε φορά, επιλέγεται αυτομάτως μία και μόνο μία είσοδος δεδομένων.

Όταν η επιλογή της επιθυμητής εισόδου δεδομένων του πολυπλέκτη

γίνεται με τέτοιον "κωδικοποιημένο" τρόπο,

τότε προκύπτει στενή συγγένεια

ανάμεσα στα κυκλώματα αποκωδικοποιητή και πολυπλέκτη:

μέσα σε κάθε πολυπλέκτη πρέπει να υπάρχει ένας αποκωδικοποιητής

που να βρίσκει πότε εμφανίζεται ο κάθε ένας συνδυασμός των bits επιλογής

και να επιλέγει την αντίστοιχη είσοδο.

Ειδικά όταν τα κυκλώματα αυτά υλοποιούνται με ένα δέντρο από διακόπτες,

τότε το ένα είναι το κατοπτρικό του άλλου!

Ο λόγος έχει να κάνει με την αμφίδρομη συμπεριφορά του διακόπτη:

ηλεκτρικό ρεύμα (και κατά συνέπεια εξίσωση τάσεων)

μπορεί να περάσει μεσα από τον διακόπτη

τόσο προς τη μία φορά όσο και προς την άλλη.

(Πάντως, όταν, σε λίγο,

θα αρχίσουμε να χρησιμοποιούμε ηλεκτρονικές "πύλες" σε chips,

οι οποίες (επίτηδες) λειτουργούν με μονόδρομη ροή της πληροφορίας

από συγκεκριμένες εισόδους προς εξόδους,

τότε ο πολυπλέκτης και ο αποκωδικοποιητής θα μοιάζουν

λίγο λιγότερο μεταξύ τους).

Το δεύτερο σχήμα δείχνει το κύκλωμα του αποκωδικοποιητή 3-σε-8 της §2.1 "γυρισμένο τα δεξιά-αριστερά" (κατοπτρισμένο), με αλλαγμένες τις εξόδους σε εισόδους δεδομένων, και με αλλαγμένον τον πόλο του διακόπτη A από τροφοδοσία σε έξοδο δεδομένων. Το νέο κύκλωμα είναι απλούστατα ένας πολυπλέκτης 8-σε-1! Οι τρείς είσοδοι επιλογής, A, B, C, των οποίων ο ρόλος έμεινε αναλλοίωτος, επιλέγουν και αποκαθιστούν, όπως και πριν, έναν από τους οκτώ δυνατούς δρόμους μεταξύ της αριστερής και της δεξιάς πλευράς του "δένδρου". Μέσα από τον επιλεγμένο δρόμο, προηγουμένως περνούσε η θετική τάση της τροφοδοσίας προς μία από τις οκτώ εξόδους· τώρα περνάει, με αντίθετη φορά, οιαδήποτε πληροφορία υπάρχει στη επιλεγμένη είσοδο δεδομένων, Data0, Data1, ..., Data7, προς την (μοναδική τώρα) έξοδο δεδομένων, DataOut.

Πριν φτάσετε στο εργαστήριο,

σχεδιάστε έναν πολυπλέκτη 16-σε-1 κατ' ανάλογο τρόπο.

Πόσες εισόδους (bits) επιλογής χρειάζεστε;

Ονομάστε τις εισόδους δεδομένων Data0 έως Data15 με τη σειρά,

και δείξτε τη θέση των διακοπτών και τις τιμές των bits επιλογής

προκειμένου να επιλεγεί η είσοδος Data13.

Στο εργαστήριο χρησιμοποιήστε την πλακέτα αποκωδικοποιητή δένδρου του πειράματος §2.2, αλλά αυτή τη φορά δίνοντας τη θετική τροφοδοσία στα φύλλα του δένδρου αντί στη ρίζα, όπως δείχνει η φωτογραφία: το κίτρινο σύρμα τώρα φέρνει την θετική τάση στην δεξιά πλευρά της πλακέτας, σε μία από τις οκτώ επαφές 000, 001, ..., 111 που τώρα παίζουν το ρόλο των εισόδων δεδομένων του πολυπλέκτη. Οι κίτρινες LED σας δείχνουν και πάλι τη θέση των τριών διακοπτών, A, B, και C. Μπορείτε να ακουμπάτε το καλώδιο τροφοδοσίας σε ένα φύλλο του δένδρου γιά λίγο, μετά να το απομακρύνετε, και μετά να το ξανακουμπάτε, σαν να στέλνετε "σήματα Μόρς". Θα βλέπετε τότε μερικές από τις κόκκινες LED να "ακούνε" τα σήματα που στέλνετε, ενώ άλλες όχι: το ποιές ακούνε και ποιές όχι το καθορίζουν τα 3 bits επιλογής, A, B, C, μέσω των διακοπτών όπως δείχνουν οι κίτρινες LED.

Με τους διακόπτες A, B, C, σε σταθερή θέση, δώστε "σήματα Μορς" σε κάθε είσοδο δεδομένων, δηλαδή σε κάθε φύλλο του δένδρου, και διαπιστώστε ότι μόνο από μία από τις 8 εισόδους καταφέρνουν να φτάσουν τα σήματά σας στη ρίζα του δένδρου, δηλαδή στην έξοδο δεδομένων. Δοκιμάστε μαζί με ένα συνάδελφό σας να δίνετε "σήματα Μορς" σε δύο διαφορετικές εισόδους δεδομένων, ταυτόχρονα, καθένας σας με ένα δικό του καλώδιο --ο ένας στην "επιλεγμένη" είσοδο, και ο άλλος σε μιάν άλλη: Τίνος από τους δύο φτάνουν τα σήματα στην έξοδο δεδομένων (στη ρίζα του δένδρου); Ποιός διακόπτης "μπλοκάρει" τα σήματα του άλλου; Μετά, αλλάξτε τους διακόπτες επιλογής, A, B, C, και ξαναδοκιμάστε τα ίδια....

3.2 Ανάδραση: Ευσταθή, Ασταθή, και Δισταθή Συστήματα

Στα επόμενα δύο πειράματα θα μελετήσουμε δύο απλά όσο και εντυπωσιακά κυκλώματα ηλεκτρονόμων. Όπως και πολλά άλλα φυσικά και τεχνητά συστήματα, αυτά εμπεριέχουν ανάδραση (feedback). Έστω ότι το σύστημα έχει μιάν είσοδο και μιάν έξοδο. Όταν δεν υπάρχει ανάδραση, η είσοδος επιδρά στην έξοδο με ορισμένο τρόπο --ιδιαίτερα μας ενδιαφέρει η πολικότητα, η ένταση, και η καθυστέρηση της επίδρασης. Όταν προστεθεί ανάδραση, η έξοδος συνδέεται πίσω στην είσοδο --είτε κατευθείαν είτε μέσω ενός άλλου συστήματος-- ούτως ώστε η έξοδος να επιδρά με τη σειρά της στην είσοδο. Το προκύπτον σύνθετο σύστημα έχει μιά νέα συμπεριφορά, που προκύπτει από την ανάδραση. Πρώτ' απ' όλα, η ανάδραση διακρίνεται σε αρνητική και σε θετική.Αρνητική λέμε την ανάδραση όταν η πολικότητά της είναι αντίθετη σε σχέση με το τι έκανε το σύστημα, δηλαδή όταν ή έξοδος αλλάζει προς μιά κατεύθυνση Α, η ανάδραση είναι τέτοια ώστε να το κάνει να κινηθεί στην αντίθετη κατεύθυνση, Β. Όταν η αρνητική ανάδραση είναι ήπια και η επίδρασή της μέσω της εισόδου του συστήματος επανεμφανίζεται στην έξοδο αρκούντως γρήγορα, τότε αυτή προκαλεί σταθεροποίηση του συστήματος και έλεγχο της συμπεριφοράς του, οπότε και μιλάμε γιά ευσταθές σύστημα. Ένα τέτοιο παράδειγμα από την καθημερινή ζωή είναι όταν είμαι κάτω από το ντους και ρυθμίζω τη θερμοκρασία του ανοιγοκλείνοντας με ήπιο και αργό τρόπο τις βρύσες του ζεστού και του κρύου. Όταν όμως η αρνητική ανάδραση είναι απότομη ή η επίδρασή της αργεί να επανεμφανιστεί στην έξοδο, τότε προκύπτει ασταθές σύστημα, το οποίο ταλαντούνται συνεχώς μεταξύ ακραίων καταστάσεων. Γιά παράδειγμα, πάλι στο ντούς, αν η αντίδραση στο ελαφρώς ζεστό νερό είναι να ανοίξω απότομα και εντελώς το κρύο, και αντίστροφα γιά το ελαφρώς κρύο νερό, τότε μάλλον θα υποφέρω συνεχώς από εναλλάξ κρύο και καυτό νερό.

Θετική λέμε την ανάδραση όταν η πολικότητά της είναι ίδια με το τι έκανε το σύστημα, δηλαδή αν ή έξοδος άλλαξε προς μία κατεύθυνση Α, η ανάδραση είναι τέτοια ώστε να το κάνει να κινηθεί ακόμα περισσότερο στην ίδια κατεύθυνση Α. Η θετική ανάδραση έχει αποκλίνοντα αποτελέσματα στο σύστημα: το πηγαίνει στα άκρα, και το αφήνει εκεί. Δεδομένου ότι πολλά συστήματα έχουν δύο ακραίες καταστάσεις, η θετική ανάδραση συνήθως τα πηγαίνει και τα αφήνει στη μία ή στην άλλη από αυτές, και τότε μιλάμε γιά δισταθή συστήματα, δηλαδή συτήματα με δύο, διαφορετικές, ευσταθείς καταστάσεις ισορροπίας (συχνά υπάρχει και μία μεσαία κατάσταση ασταθούς ισορροπίας). Τα δισταθή συστήματα μπορούμε να τα χρησιμοποιήσουμε γιά αποθήκευση πληροφορίας: έχουν μνήμη και "θυμούνται" σε ποιάν από τις καταστάσεις ευσταθούς ισορροπίας τους τα αφήσαμε. Τα ασταθή συστήματα μπορούμε να τα χρησιμοποιήσουμε γιά τη δημιουργία "ρολογιών" μέτρησης του χρόνου (όταν η περίοδος ταλάντωσής τους είναι αρκούντως προβλέψιμη ή ελέγξιμη).

Πείραμα 3.3: Ταλαντωτής με Ηλεκτρονόμο

Πείραμα 3.3: Ταλαντωτής με Ηλεκτρονόμο

Ο ηλεκτρονόμος στο κύκλωμα δεξιά ελέγχει τον εαυτό του

χρησιμοποιώντας αρνητική ανάδραση:

όταν το πηνίο είναι αδρανές,

ο διακόπτης του ηλεκτρονόμου τροφοδοτεί το πηνίο με ρεύμα,

ενεργοποιώντας το έτσι·

όταν όμως το πηνίο ενεργοποιηθεί,

ο διακόπτης του ηλεκτρονόμου διακόπτει το ρεύμα του πηνίου,

προκαλώντας έτσι την αδρανοποίησή του.

Δεδομένου ότι η "διόρθωση" που προκαλεί η αρνητική ανάδραση

είναι ψηφιακή, δηλαδή ακραία,

και όχι ήπια και προοδευτική (αναλογική),

το κύκλωμα αυτό είναι ασταθές,

δηλαδή ταλαντούται,

μ' άλλα λόγια το πηνίο θα αναβοσβήνει συνεχώς,

και ο διακόπτης θα ανοιγοκλείνει, αντίστοιχα συνεχώς.

Προσοχή:

επειδή ο ηλεκτρονόμος αναβοσβήνει πολύ γρήγορα,

φθείρεται αντίστοιχα γρήγορα.

Γιά να αποφευχθεί σημαντική φθορά του,

μην τον αφήνετε να ταλαντούται επί πολλή ώρα.

Γιά το σκοπό αυτό προσθέσαμε το διακόπτη "GO":

ο ηλεκτρονόμος ταλαντούται μόνο όταν ο "GO" είναι πατημένος·

μην πατάτε επί πολλή ώρα τον "GO".

Στο εργαστήριο, κατασκευάστε το κύκλωμα αυτό,

και δοκιμάστε το εν συντομία.

Πριν το εργαστήριο, κάντε μιά γραφική αναπαράσταση της συμπεριφοράς του ηλεκτρονόμου. Βάλτε στον οριζόντιο άξονα τον χρόνο, και στον κατακόρυφο άξονα το ρεύμα του πηνίου. Το ρεύμα του πηνίου είναι 100 mA όταν ο διακόπτης του ηλεκτρονόμου κάνει επαφή επάνω, και 0 όταν αυτός δεν κάνει επαφή επάνω. Όταν ανάβει το πηνίο (περνάει ρεύμα μέσα από αυτό), η επαφή διακόπτεται μετά από καθυστέρηση 5 ms. Όταν σβήνει το πηνίο (δεν περνάει ρεύμα), η επαφή αποκαθίσταται μετά από καθυστέρηση 3 ms. Οι καθυστερήσεις αυτές οφείλονται στην αδράνεια των κινουμένων μερών του ηλεκτρονόμου (οι αριθμητικές τιμές είναι πλασματικές, αλλά της ίδιας τάξης μεγέθους με τις αληθινές). Θεωρήστε ότι ο διακόπτης GO πατιέται τη χρονική στιγμή t=0, και δείξτε τη συμπεριφορά του ηλεκτρονόμου σαν συνάρτηση του χρόνου, από το χρόνο 0 μέχρι το χρόνο t = 25 ms. Ποιά είναι η περίοδος και ποιά η συχνότητα ταλάντωσης του ηλεκτρονόμου;

Πείραμα 3.4: Μνήμη "RS Flip-Flop" με Ηλεκτρονόμο

Πείραμα 3.4: Μνήμη "RS Flip-Flop" με Ηλεκτρονόμο

Ο ηλεκτρονόμος δεξιά ελέγχει τον εαυτό του με θετική ανάδραση:

όταν το πηνίο είναι αδρανές,

ο διακόπτης του ηλεκτρονόμου δεν τροφοδοτεί το πηνίο με ρεύμα,

κι έτσι το πηνίο παραμένει αδρανές·

όταν το πηνίο ενεργοποιηθεί (εξωτερικά),

ο ίδιος διακόπτης τροφοδοτεί το πηνίο με ρεύμα,

κι έτσι το πηνίο παραμένει ενεργοποιημένο.

Άρα, το κύκλωμα αυτό είναι δισταθές:

αν ήταν αδρανές παραμένει αδρανές,

και αν ήταν ενεργό παραμένει ενεργό,

δηλαδή αποτελεί ένα στοιχείο μνήμης

χωρητικότητας ενός bit:

μπορεί να αποθηκεύσει και να θυμάται μία δυαδική ψηφιακή τιμή

(αδρανές ή ενεργό).

Το ισοδύναμο αυτού του κυκλώματος,

αλλά φτιαγμένο από transistors,

λέγεται "flip-flop".

Όλα αυτά ισχύουν όσο δεν υπάρχει εξωτερική επίδραση,

δηλαδή όσο δεν πατιέται κανένας από τους διακόπτες

"SET" και "RESET".

Εάν ο ηλεκτρονόμος είναι αδρανής και πατηθεί το κουμπί SET, τότε παρακάμπτεται ο διακόπτης του ηλεκτρονόμου, και τροφοδοτείται με ρεύμα το πηνίο, με συνέπεια να ενεργοποιηθεί ο ηλεκτρονόμος. Μόλις ενεργοποιηθεί, ο διακόπτης του ηλεκτρονόμου αρχίζει να παρέχει και αυτός ρεύμα στο πηνίο, οπότε πλέον δεν είναι ανάγκη να παραμένει πατημένο το SET προκειμένου να παραμείνει ενεργός ο ηλεκτρονόμος. Άρα, το κουμπί SET "θέτει" (set) το στοιχείο μνήμης στην ενεργή κατάσταση, δηλαδή γράφει στο στοιχείο αυτό τη μία από τις τιμές που αυτό μπορεί να κρατήσει --ας πούμε την τιμή "1".

Εάν ο ηλεκτρονόμος είναι ενεργός και πατηθεί το κουμπί RESET, τότε διακόπτεται η τροφοδοσία ρεύματος στον ηλεκτρονόμο, και επομένως αυτός πηγαίνει στην αδρανή κατάσταση, και παραμένει εκεί ακόμα κι αν αφεθεί το κουμπί RESET (αρκεί να μην είναι πατημένο ταυτόχρονα και το SET). Άρα, το κουμπί RESET "επαναφέρει" (reset) το στοιχείο μνήμης στην αδρανή κατάσταση, δηλαδή γράφει στο στοιχείο αυτό την άλλη από τις τιμές που αυτό μπορεί να κρατήσει --ας πούμε την τιμή "0". Από τα αρχικά των λέξεων RESET και SET, το flip-flop αυτό λέγεται τύπου "RS".

Πριν το εργαστήριο, εξηγήστε γραπτά τι θα συμβεί εάν πατηθούν ταυτόχρονα τα SET και RESET: ποιό υπερισχύει; γιατί; Εάν αφεθεί πρώτο το SET και μετά το RESET, σε ποιά κατάστση θα μείνει το στοιχείο μνήμης; Εάν αφεθούν με αντίστροφη σειρά, τι θα γίνει; Στο εργαστήριο, κατασκευάστε το κύκλωμα και ελέγξτε τη λειτουργία του. Μετά, πατήστε και το SET και το RESET, και προσπαθήστε να τα αφήσετε και τα δύο "ταυτόχρονα": τι θα συμβεί; μπορείτε να πετύχετε πραγματικά απόλυτο "ταυτοχρονισμό";

3.5 Λογικές Πύλες: Συνθέσιμα, Μονόδρομα Κυκλώματα

Όπως είπαμε στην § 2.11,

χρειαζόμαστε ψηφιακά κυκλώματα συνθέσιμα,

που να μπορούμε δηλαδή να τα συνδέουμε ελεύθερα το ένα με το άλλο

προκειμένου έτσι να φτιάχνουμε ολοένα και συνθετότερα ψηφιακά συστήματα.

Πρέπει επομένως η σύμβαση αναπαράστασης των ψηφιακών τιμών

να είναι ίδια στις εισόδους και στις εξόδους,

ώστε η κάθε έξοδός τους να μπορεί να τροφοδοτήσει κατευθείαν

μία ή περισσότερες εισόδους άλλων τέτοιων κυκλωμάτων.

Τέτοια ψηφιακά κυκλώματα που υλοποιούν τις στοιχειώδεις λογικές πράξεις

ΚΑΙ,

Ή,

ΟΧΙ

(καθώς και μερικές άλλες παρεμφερείς)

τα λέμε Λογικές Πύλες,

και τα συμβολίζουμε όπως φαίνεται στο σχήμα.

Ειδικά γιά τη λογική αντιστροφή,

το κατ' εξοχή σύμβολό της είναι ο μικρός κύκλος στη μύτη του τριγώνου

--το τρίγωνο, κατά βάση, συμβολίζει ενίσχυση.

Όπως είπαμε στην § 2.11,

χρειαζόμαστε ψηφιακά κυκλώματα συνθέσιμα,

που να μπορούμε δηλαδή να τα συνδέουμε ελεύθερα το ένα με το άλλο

προκειμένου έτσι να φτιάχνουμε ολοένα και συνθετότερα ψηφιακά συστήματα.

Πρέπει επομένως η σύμβαση αναπαράστασης των ψηφιακών τιμών

να είναι ίδια στις εισόδους και στις εξόδους,

ώστε η κάθε έξοδός τους να μπορεί να τροφοδοτήσει κατευθείαν

μία ή περισσότερες εισόδους άλλων τέτοιων κυκλωμάτων.

Τέτοια ψηφιακά κυκλώματα που υλοποιούν τις στοιχειώδεις λογικές πράξεις

ΚΑΙ,

Ή,

ΟΧΙ

(καθώς και μερικές άλλες παρεμφερείς)

τα λέμε Λογικές Πύλες,

και τα συμβολίζουμε όπως φαίνεται στο σχήμα.

Ειδικά γιά τη λογική αντιστροφή,

το κατ' εξοχή σύμβολό της είναι ο μικρός κύκλος στη μύτη του τριγώνου

--το τρίγωνο, κατά βάση, συμβολίζει ενίσχυση.

Τα σύμβολα αυτά υποδεικνύουν πάντα κυκλώματα με

μονόδρομη ροή της πληροφορίας

(δηλαδή της αιτίας αλλαγών κατάστασης)

από τις εισόδους τους (αριστερά στο σχήμα)

προς τις εξόδους τους (δεξιά στο σχήμα),

και ποτέ αντίστροφα.

Με άλλα λόγια, στα κυκλώματα αυτά,

η τιμή της εξόδου τους καθορίζεται

από τις τιμές των εισόδων τους (και μόνο),

ενώ οι τιμές των εισόδων τους ουδόλως επηρρεάζονται

από το τι συμβαίνει στις άλλες εισόδους ή στις εξόδους τους.

Αυτό μας προφυλάσσει από τους κινδύνους γιά τους οποίους

--όποιος ενδιαφέρεται-- μπορεί να διαβάσει στο προαιρετικό φυλλάδιο

extra03_relayLogic.html,

έστω και εάν, μερικές φορές, μας κοστίζει περισσότερο απ' όσο άλλα,

πιό "επικίνδυνα" κυκλώματα που θα βρεί ο ενδιαφερόμενος αναγνώστης εκεί.

Οι παραπάνω λογικές πύλες μπορούν να υλοποιηθούν με ηλεκτρονόμους (§ 2.12), όπως φαίνεται δίπλα, αν και σήμερα σπανιότατα χρησιμοποιούνται τέτοιες υλοποιήσεις. Εδώ, η αναπαράσταση των ψηφιακών τιμών είναι: "0" = ανοικτό κύκλωμα (μηδέν ρεύμα), και "1" = ψηλή τάση με δυνατότητα παροχής επαρκούς ρεύματος. Όπως πάντα, η βασική ιδέα της πράξης ΚΑΙ είναι η σύνδεση διακοπτών εν σειρά, ενώ γιά την πράξη Ή θέλουμε διακόπτες εν παραλλήλω. Παρατηρήστε ότι και τα τρία αυτά κυκλώματα εγγυώνται τη μονόδρομη ροή της πληροφορίας που προδιαγράψαμε παραπάνω, αφού το κύκλωμα των διακοπτών των ηλεκτρονόμων (έξοδος πύλης) είναι αδύνατον να επηρρεάσει την τάση ή το ρεύμα του πηνίου τους (είσοδοι πύλης).

Όταν γράφουμε τις λογικές πράξεις σε μορφή κειμένου ή εξισώσεων, επειδή οι λέξεις και, ή, όχι πιάνουν πολύ χώρο, έχουν υιοθετηθεί διεθνώς άλλα, συντομότερα σύμβολα, όπως στο αρχικό σχήμα της παραγράφου αυτής, δεξιά από τα σύμβολα των πυλών. Στη γλώσσα προγραμματισμού C, καθώς και στη γλώσσα περιγραφής υλικού Verilog, η πράξη (bitwise) AND συμβολίζεται με "&", η πράξη (bitwise) OR συμβολίζεται με "|", και η πράξη (bitwise) ΝΟΤ συμβολίζεται με "~". Σε βιβλία και κείμενα θεωρίας ψηφιακής σχεδίασης, η πράξη AND συμβολίζεται με μία τελεία --ή και χωρίς αυτήν-- όπως ο πολλαπλασιασμός, η δε πράξη OR συμβολίζεται με ένα σταυρό, όπως και η πρόσθεση. Τη συνήθεια αυτή πρέπει να τη δεί κανείς σαν απλό συμβολισμό, χωρίς κανένα περαιτέρω νόημα ότι δήθεν υπάρχει ομοιότητα ή ταύτιση των λογικών πράξεων AND/OR με τις αριθμητικές πράξεις πολλαπλασιασμού/πρόσθεσης --πρόκειται γιά εντελώς διαφορετικά πράγματα, και απλώς υιοθετούμε το ίδιο σύμβολο γιά λόγους τυπογραφίας και μόνο. Η πράξη ΝΟΤ συμβολίζεται με μία μπάρα πάνω από το όρισμά της· όταν τυπογραφικοί λόγοι καθιστούν δύσκολη τη χρήση μπάρας, χρησιμοποιείται εναλλακτικά ο συμβολισμός "τονούμενο" (prime).

3.6 Λογικές Πύλες σε Τεχνολογία CMOS

Φυσικά, οι υπολογιστές δεν φτιάχνονται πιά με ηλεκτρονόμους αλλά με ολοκληρωμένα κυκλώματα. Τα περισσότερα ολοκληρωμένα κυκλώματα, σήμερα, φτιάχνονται με την τεχνολογία CMOS (complementary MOS - συμπληρωματικά MOS). Τη βάση της τεχνολογίας αυτής αποτελούν τα transistors τύπου "MOS FET" (metal - oxide - semiconductor field-effect transistor): transistor επίδρασης πεδίου τύπου μέταλλο - οξείδιο - ημιαγωγός. Κάθε transistor έχει ένα ηλεκτρόδιο ελέγχου ("πύλη") και δύο ηλεκτρόδια που είναι οι άκρες ενός ημιαγώγιμου "καναλιού". Προσοχή να μην συγχέουμε την "πύλη" του transistor με τις "λογικές πύλες" της παραγράφου 3.5 --πρόκειται γιά δύο άσχετες μεταξύ τους χρήσεις του ίδιου όρου. Η πύλη βρίσκεται "πάνω" από το κανάλι, και επιδρά στην αγωγιμότητά του μέσω ηλεκτρικού πεδίου, χωρίς να κάνει ηλεκτρική επαφή με το κανάλι· γι' αυτό η πύλη δεν διαρρέεται ποτέ από ρεύμα, κι έτσι η τεχνολογία CMOS μπορεί να δώσει chips χαμηλής κατανάλωσης ενέργειας.

Η τεχνολογία CMOS έχει δύο "συμπληρωματικά" είδη transistors:

τα τύπου NMOS (negative-channel MOS) με "αρνητικό" κανάλι,

και τα τύπου PMOS (positive-channel MOS) με "θετικό" κανάλι.

Στα NMOS, το κανάλι δημιουργείται

από ελεύθερα ηλεκτρόνια (αρνητικούς φορείς)

τα οποία προσελκύει εκεί η τάση της πύλης·

επειδή τα ηλεκτρόνια έλκονται από θετικές τάσεις,

οι ψηλές τάσεις πύλης αυξάνουν την αγωγιμότητα των καναλιών NMOS.

Στα PMOS, το κανάλι δημιουργείται

από ελεύθερες "οπές" (έλλειψη ηλεκτρονίων - θετικοί φορείς)·

επειδή οι οπές έλκονται από αρνητικές τάσεις,

η αγωγιμότητα των καναλιών PMOS

αυξάνει με χαμηλές τάσεις πύλης, ενώ μειώνεται με τις ψηλές.

Στα ψηφιακά κυκλώματα, τα transistors χρησιμοποιούνται σαν διακόπτες, όπως φαίνεται στο σχήμα. Τα NMOS συμπεριφέρονται σαν "θετικοί" διακόπτες: με ψηλές τάσεις πύλης το κανάλι τους άγει, ενώ με χαμηλές τάσεις πύλης το κανάλι τους γίνεται σαν ανοικτό κύκλωμα. Αντίθετα, τα PMOS συμπεριφέρονται σαν "αρνητικοί" διακόπτες: το κανάλι τους άγει με χαμηλές τάσεις πύλης, και δεν άγει με ψηλές τάσεις. Το σύμβολο του PMOS, όπως φαίνεται στο σχήμα, έχει έναν μικρό κύκλο γιά να μας θυμίζει αυτή την "αρνητική" συμπεριφορά. Επομένως, τα transistors μπορούν να χρησιμοποιηθούν όπως και οι ηλεκτρονόμοι. Κάθε διακόπτης του ηλεκτρονόμου έχει δύο επαφές· το transistor NMOS παίζει το ρόλο της "κάτω" (θετικής) επαφής, και το PMOS της "επάνω" (αρνητικής) επαφής. Η διαφορά με τους ηλεκτρονόμους είναι στη σύμβαση αναπαράστασης των ψηφιακών τιμών: οι είσοδοι (πύλες) των transistors είναι ευαίσθητες στην τάση και όχι στο ρεύμα· έτσι, το μεν 1 παραμένει σαν "υψηλή τάση", αλλά το 0 πρέπει να γίνει "χαμηλή τάση", αντί "ανοικτό κύκλωμα" που ήταν. Κατά συνέπεια, κάθε λογική πύλη πρέπει να περιλαμβάνει όχι μόνο τα κυκλώματα που τροφοδοτούν την έξοδο με ψηλή τάση στις επιθυμητές προς τούτο περιπτώσεις --τα οποία ήδη υπήρχαν-- αλλά και κυκλώματα που να τροφοδοτούν την έξοδο με χαμηλή τάση στις υπόλοιπες περιπτώσεις.

Στο επόμενο σχήμα φαίνεται η κατασκευή ενός αντιστροφέα σε CMOS·

αποτελείται από ένα transistor NMOS κι ένα PMOS,

ελεγχόμενα και τα δύο από την τάση εισόδου.

Χαμηλή τάση εισόδου προκαλεί άναμα του PMOS και σβήσιμο του NMOS,

οπότε η έξοδος συνδέεται αγώγιμα με τη θετική τροφοδοσία

και παίρνει ψηλή τάση.

Αντίθετα, ψηλή είσοδος προκαλεί άναμα του NMOS και σβήσιμο του PMOS,

οπότε η έξοδος συνδέεται αγώγιμα με τη γείωση και παίρνει χαμηλή τάση.

Παρατηρήστε ότι η είσοδος δεν συνδέεται αγώγιμα με κανέναν άλλο κόμβο,

αφού τροφοδοτεί αποκλειστικά και μόνο πύλες από transistors,

και αφού αυτές, όπως είδαμε, είναι ηλεκτρικά μονωμένες

από όλους τους γύρω τους ημιαγωγούς.

Έτσι εξασφαλίζεται η μονόδρομη ροή πληροφορίας,

από την είσοδο προς την έξοδο και ποτέ αντίστροφα,

όπως προδιαγράψαμε στην παράγραφο 3.5.

Στο επόμενο σχήμα φαίνεται η κατασκευή ενός αντιστροφέα σε CMOS·

αποτελείται από ένα transistor NMOS κι ένα PMOS,

ελεγχόμενα και τα δύο από την τάση εισόδου.

Χαμηλή τάση εισόδου προκαλεί άναμα του PMOS και σβήσιμο του NMOS,

οπότε η έξοδος συνδέεται αγώγιμα με τη θετική τροφοδοσία

και παίρνει ψηλή τάση.

Αντίθετα, ψηλή είσοδος προκαλεί άναμα του NMOS και σβήσιμο του PMOS,

οπότε η έξοδος συνδέεται αγώγιμα με τη γείωση και παίρνει χαμηλή τάση.

Παρατηρήστε ότι η είσοδος δεν συνδέεται αγώγιμα με κανέναν άλλο κόμβο,

αφού τροφοδοτεί αποκλειστικά και μόνο πύλες από transistors,

και αφού αυτές, όπως είδαμε, είναι ηλεκτρικά μονωμένες

από όλους τους γύρω τους ημιαγωγούς.

Έτσι εξασφαλίζεται η μονόδρομη ροή πληροφορίας,

από την είσοδο προς την έξοδο και ποτέ αντίστροφα,

όπως προδιαγράψαμε στην παράγραφο 3.5.

Στο τρίτο σχήμα, στα αριστερά, φαίνεται η κατασκευή των πυλών "ΟΧΙ-ΚΑΙ" (NAND) και "ΟΥΤΕ" (NOR - ΟΧΙ-Ή) σε CMOS. Κάθε πύλη έχει ένα "δίκτυο καθέλκυσης" (pull-down net), αποτελούμενο από transistors τύπου NMOS, γιά να τροφοδοτεί την έξοδο με χαμηλή τάση, κι ένα δυϊκό "δίκτυο ανέλκυσης" (pull-up net), αποτελούμενο από transistors τύπου PMOS, γιά την τροφοδότηση με ψηλή τάση· ο δυϊσμός έγκειται στην ανταλλαγή μεταξύ συνδεσμολογίας σειράς (ΚΑΙ) και παράλληλης (Ή), καθώς και στην ανταλλαγή μεταξύ transistors τύπων NMOS και PMOS. Εάν χρησιμοποιούσαμε transistors NMOS γιά ανέλκυση και PMOS γιά καθέλκυση θα μπορούσαμε να φτιάξουμε πύλες AND και OR· όμως, δυστυχώς, τα NMOS λειτουργούν σαν καλοί διακόπτες μόνο όταν η τάση καναλιού τους είναι χαμηλή, δηλαδή μόνο στα δίκτυα καθέλκυσης, και τα PMOS μόνο με ψηλές τάσεις καναλιού, δηλαδή μόνο σε δίκτυα ανέλκυσης. Στο δεξί μέρος του σχήματος φαίνεται η συμπεριφορά των δύο κυκλωμάτων γιά τους 4 συνδυασμούς τιμών των δύο εισόδων, A και B, επιβεβαιώνοντας έτσι ότι αυτά υλοποιούν τις λογικές συναρτήσεις (AB)', δηλαδή NAND, και (A+B)', δηλαδή NOR. Όπως βλέπουμε, πάντα, ένα και μόνον ένα από τα δίκτυα ανέλκυσης και καθέλκυσης είναι αγώγιμο, καθορίζοντας έτσι την τάση εξόδου, ενώ το άλλο δίκτυο είναι αποκομμένο (ανοικτό κύκλωμα), ούτως ώστε να μην επηρρεάζει την έξοδο και να μην καταναλώνει ενέργεια (ρεύμα τροφοδοσίας).

3.7 Τα Chips του Εργαστηρίου

Προηγούμενες χρονιές, κάθε φοιτητής παραλάμβανε ένα σακκουλάκι με chips όπως αυτό στη φωτογραφία δεξιά, και με αυτά έκανε τα πειράματά του μέχρι τέλους του μαθήματος και στη συνέχεια τα επέστρεφε. Φέτος, αντίθετα, τα chips γιά το κάθε εργαστήριο θα βρίσκονται στην πλακέτα έτοιμα: χρησιμοποιήστε τα προσεκτικά, μην τα χαλάσετε ή κάψετε, και αφήστε τα στην πλακέτα, στη θέση που τα βρήκατε, όταν τελειώσετε (αλλά τα σύρματα της συνδεσμολογίας σας πρέπει να τα βγάλετε και τακτοποιήσετε). Το σακκουλάκι αυτό περιέχει όλα τα chips που θα χρειαστείτε

γιά όλες τις εργαστηριακές ασκήσεις μέχρι το τέλος του μαθήματος,

εκτός από τα chips μνήμης SRAM του εργαστηρίου 9 τα οποία είναι ακριβά.

Τα chips αυτά πρέπει να τα προσέχετε διότι είναι ευπαθή,

όπως θα πούμε αμέσως πιό κάτω.

Στο εργαστήριο υπάρχει ένα μηχάνημα ελέγχου των chips,

το οποίο μας λέει άν ένα chip που του συνδέομε

λειτουργεί σωστά ή είναι χαλασμένο.

Αν υποπτεύεστε ότι έχετε κάψει ένα από τα chips σας

(και γι' αυτό δεν σας δουλεύει η άσκηση),

μπορείτε να απευθυνθείτε στον επόπτη-βοηθό του εργαστηρίου σας

προκειμένου εκείνος να ελέγξει με το μηχανημα αυτό το chip σας·

όμως, τέτοιους ελέγχους πρέπει να φροντίσετε να ζητάτε σπάνια,

διότι άλλως θα δημιουργείται μακριά ουρά αναμονής και καθυστερήσεις

από τους πολλούς τέτοιους ελέγχους.

Το σακκουλάκι που παίρνει καθένας περιέχει τα εξής chips,

με τη σειρά από κάτω-αριστερά προς τα επάνω δεξιά:

Το σακκουλάκι αυτό περιέχει όλα τα chips που θα χρειαστείτε

γιά όλες τις εργαστηριακές ασκήσεις μέχρι το τέλος του μαθήματος,

εκτός από τα chips μνήμης SRAM του εργαστηρίου 9 τα οποία είναι ακριβά.

Τα chips αυτά πρέπει να τα προσέχετε διότι είναι ευπαθή,

όπως θα πούμε αμέσως πιό κάτω.

Στο εργαστήριο υπάρχει ένα μηχάνημα ελέγχου των chips,

το οποίο μας λέει άν ένα chip που του συνδέομε

λειτουργεί σωστά ή είναι χαλασμένο.

Αν υποπτεύεστε ότι έχετε κάψει ένα από τα chips σας

(και γι' αυτό δεν σας δουλεύει η άσκηση),

μπορείτε να απευθυνθείτε στον επόπτη-βοηθό του εργαστηρίου σας

προκειμένου εκείνος να ελέγξει με το μηχανημα αυτό το chip σας·

όμως, τέτοιους ελέγχους πρέπει να φροντίσετε να ζητάτε σπάνια,

διότι άλλως θα δημιουργείται μακριά ουρά αναμονής και καθυστερήσεις

από τους πολλούς τέτοιους ελέγχους.

Το σακκουλάκι που παίρνει καθένας περιέχει τα εξής chips,

με τη σειρά από κάτω-αριστερά προς τα επάνω δεξιά:

- 7402: τέσσερεις (4) πύλες NOR 2 εισόδων (1 chip, κόστους 42 ευρωλεπτών) http://www.ti.com/lit/ds/symlink/sn74ls02.pdf

- 7404: έξι (6) αντιστροφείς (πύλες NOT) (1 chip, κόστους 42 ευρωλεπτών) http://www.ti.com/lit/ds/symlink/sn74ls04.pdf

- 7408: τέσσερεις (4) πύλες AND 2 εισόδων (2 chips, κόστους 42 ευρωλεπτών το ένα) http://www.ti.com/lit/ds/symlink/sn74ls08.pdf

- 7432: τέσσερεις (4) πύλες OR 2 εισόδων (2 chips, κόστους 42 ευρωλεπτών το ένα) http://www.ti.com/lit/ds/symlink/sn74ls32.pdf

- 74283: τετράμπιτος (4-bit) πλήρης αθροιστής (full adder) (1 chip, κόστους 59 ευρωλεπτών) http://www.ti.com/lit/ds/symlink/sn54ls283.pdf

- 7486: τέσσερεις (4) πύλες αποκλειστικού-Ή (XOR) 2 εισόδων (2 chips, κόστους 47 ευρωλεπτών το ένα) http://www.ti.com/lit/ds/symlink/sn54ls86a.pdf

- 4511: αποκωδικοποιητής BCD σε ένδειξη 7 τμημάτων (1 chip, κόστους 59 ευρωλεπτών) http://www.ti.com/lit/ds/symlink/cd4511b.pdf

- 74257: τέσσερεις (4) πολυπλέκτες (MUX) 2-σε-1 (1 chip, κόστους 42 ευρωλεπτών) http://www.ti.com/lit/ds/symlink/sn74ls257b.pdf

- 74573: οκτώ (8) μανταλωτές (Latch) με τρικατάστατες εξόδους (2 chips, κόστους 36 ευρωλεπτών το ένα) https://assets.nexperia.com/documents/data-sheet/74HC_HCT573.pdf

- 74574: οκτώ (8) ακμοπυροδότητα Flip-Flops τύπου D με τρικατάστατες εξόδους (1 chip, κόστους 65 ευρωλεπτών) http://www.ti.com/lit/ds/symlink/sn74als574b.pdf

Τα chips αυτά είναι μακρόστενα. Τα μικρότερα από αυτά έχουν 14 ακροδέκτες ("ποδαράκια" - pins) το καθένα, μερικά έχουν 16 ακροδέκτες, και τα μεγαλύτερα έχουν 20. Οι ακροδέκτες βρίσκονται κατά μήκος των δύο μακρυών πλευρών τους --μισοί στη μία και μισοί στην άλλη ("περίβλημα δύο σειρών στη γραμμή" - dual in-line package - DIP). Τα chips αυτά μπαίνουν στην πλακέτα συνδέσεων (§ 0.5) κατά μήκος των κεντρικών αυλακιών της, όπως φαίνεται στο σχήμα δίπλα. Κάθε chip έχει, στη μία στενή πλευρά του, ένα χαρακτηριστικό σημαδάκι (εγκοπή, βαθούλωμα) το οποίο καθορίζει τον προσανατολισμό του chip και τη θέση του κάθε ακροδέκτη του. Όταν η εγκοπή αυτή τοποθετηθεί αριστερά (κοιτώντας το chip από επάνω), τότε η αρίθμηση των pins γίνεται όπως στο σχήμα. Γιά να λειτουργήσουν τα chips χρειάζονται ηλεκτρική τροφοδοσία --θετικό και αρνητικό πόλο. Τα chips αυτού του εργαστηρίου, και τα περισσότερα από τα chips στο σακκουλάκι (αλλά όχι όλα!), παίρνουν τον αρνητικό πόλο της τροφοδοσίας (τη "γείωση") στον κάτω δεξιό ακροδέκτη και τον θετικό πόλο της τροφοδοσίας στον πάνω αριστερό ακροδέκτη, όταν η χαρακτηριστική εγκοπή είναι αριστερά. Τις συνδέσεις αυτές πρέπει να τις κάνετε εσείς, γιά καθένα από τα chips. Η τάση τροφοδοσίας τους είναι 5 Volt (σε αντίθεση με τα περισσότερα σύγχρονα chips που χρειάζονται χαμηλότερες τάσεις τροφοδοσίας --3.3, ή 2.5, ή 1.8 Volt ή άλλες).

Κάθε chip γράφει επάνω τον τύπο του και άλλες πληροφορίες. Η επιγραφή είναι δυσαναγνωστη σε μερικά chips, αλλά διαβάζεται ευκολότερα υπό ορισμένες γωνίες, ειδικά αν η επιφάνεια του chip δεν ανακλά το φωτισμό κατ' ευθείαν στα μάτια σας (δεν γυαλίζει). Στα περισσότερα chips που θα πάρετε, μπροστά από τον χαρακτηριστικό κωδικό 74 υπάρχουν ένα ή δύο γράμματα, συνήθως "SN" που υποδεικνύει ώς κατασκευάστρια εταιρεία την Texas Instruments, ή "M" που υποδεικνύει την εταιρεία ST Microelectronics. Μετά τον χαρακτηριστικό κωδικό 74 και πριν τον κωδικό του τύπου του chip αυτόν καθεαυτόν (π.χ. "02" γιά NOR, "04" γιά NOT, "08" γιά AND, κ.ο.κ.), υπάρχουν δύο ή τρία γράμματα που υποδεικνύουν την τεχνολογία κατασκευής και το είδος κυκλώματος της πύλης: συνήθως "LS" (διπολικά transistors, κύκλωμα τύπου "Low-Power Shottky"), "ALS" (Advanced LS), ή "HC" (transistors MOS, κύκλωμα τύπου High-speed CMOS). Όπως είπαμε στην προηγούμενη παράγραφο 3.6, τα περισσότερα σημερινά chips είναι τεχνολογιάς CMOS, και περιέχουν εκατομμύρια (ή τουλάχιστο πολλές χιλιάδες) transistors το καθένα. Όμως, τα chips του εργαστηρίου μας είναι κλασσικά ("παλαιοντολογικά") chips της δεκαετίας του '60, με λίγες μόνο πύλες μέσα το καθένα, ή τουλάχιστο νεότερες, συμβατές παραλλαγές τους. Τα κλασσικά chips της δεκαετίας του '60 δεν ήταν κατασκευασμένα σε τεχνολογία CMOS --η CMOS είναι μεταγενέστερη τεχνολογία-- αλλά με "διπολικά" transistors, σε μιά παλιά τεχνολογία ονόματι "TTL"· τα chips "LS" και "ALS" είναι τέτοια, ενώ τα "HC" είναι νεότερες, συμβατές παραλλαγές των chips εκείνων σε τεχνολογία CMOS.

Πείραμα 3.8: Γνωριμία με το Chip 7408 (4 πύλες AND)

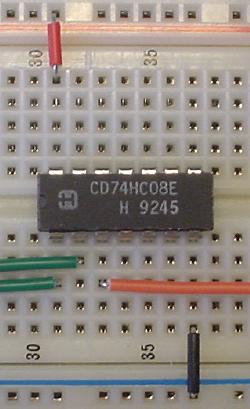

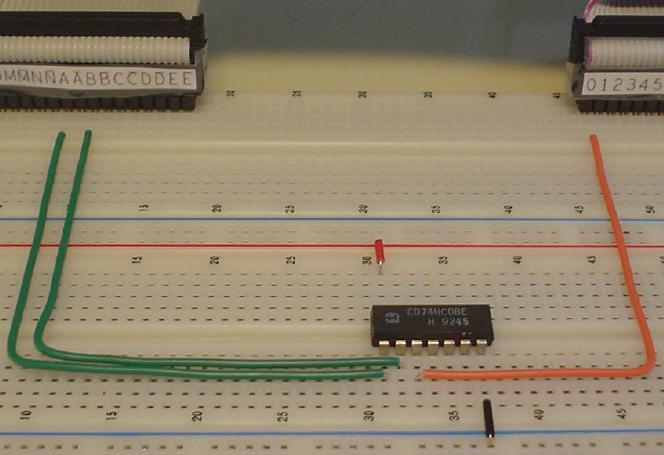

Οι φωτογραφίες και το κύκλωμα

δείχνουν πώς τοποθετείται ένα chip στην πλακέτα συνδέσεων

και πώς τίθεται σε λειτουργία·

η μικρή φωτογραφία αποτελεί μεγέθυνση

της κεντρικής περιοχής της μεγάλης φωτογραφίας.

Πρόκειται απλούστατα γιά μιάν από τις τέσσερεις πύλες ΚΑΙ

που περιέχονται σε ένα chip 7408,

της οποίας τροφοδοτούμε τις δύο εισόδους

από τους διακόπτες A και B της πλακέτας εισόδων/εξόδων,

και της οποίας συνδέουμε την έξοδο

σε μιά ενδεικτική λυχνία της ίδιας πλακέτας,

Οι φωτογραφίες και το κύκλωμα

δείχνουν πώς τοποθετείται ένα chip στην πλακέτα συνδέσεων

και πώς τίθεται σε λειτουργία·

η μικρή φωτογραφία αποτελεί μεγέθυνση

της κεντρικής περιοχής της μεγάλης φωτογραφίας.

Πρόκειται απλούστατα γιά μιάν από τις τέσσερεις πύλες ΚΑΙ

που περιέχονται σε ένα chip 7408,

της οποίας τροφοδοτούμε τις δύο εισόδους

από τους διακόπτες A και B της πλακέτας εισόδων/εξόδων,

και της οποίας συνδέουμε την έξοδο

σε μιά ενδεικτική λυχνία της ίδιας πλακέτας,

προκειμένου να ελέγξουμε τη λειτουργία της

γιά τους 4 διαφορετικούς συνδυασμούς τιμών των δύο εισόδων A και B.

Αφού πρώτα διαβάσετε τις οδηγίες της επομένης παραγράφου,

κατασκευάστε --με σβηστή την τροφοδοσία-- το κύκλωμα αυτό

(και μην ξεχάστε, πρώτ' απ' όλα, τις συνδέσεις τροφοδοσίας!),

δώστε όλους τους συνδυασμούς τιμών εισόδων,

και ελέγξτε την ορθότητα της εξόδου.

Στο τέλος σβήστε την τροφοδοσία

αλλά μην βγάλετε το chip ή τις συνδέσεις τροφοδοσίας του:

θα σας χρειαστούν γιά το επόμενο πείραμα.

προκειμένου να ελέγξουμε τη λειτουργία της

γιά τους 4 διαφορετικούς συνδυασμούς τιμών των δύο εισόδων A και B.

Αφού πρώτα διαβάσετε τις οδηγίες της επομένης παραγράφου,

κατασκευάστε --με σβηστή την τροφοδοσία-- το κύκλωμα αυτό

(και μην ξεχάστε, πρώτ' απ' όλα, τις συνδέσεις τροφοδοσίας!),

δώστε όλους τους συνδυασμούς τιμών εισόδων,

και ελέγξτε την ορθότητα της εξόδου.

Στο τέλος σβήστε την τροφοδοσία

αλλά μην βγάλετε το chip ή τις συνδέσεις τροφοδοσίας του:

θα σας χρειαστούν γιά το επόμενο πείραμα.

3.9 Πώς να (μην) Καταστρέψετε ή Κάψετε τα Chips σας...

Εάν επιθυμείτε να κάψετε ή καταστρέψετε ένα ή περισσότερα από τα chips σας, ούτως ώστε να έχετε στη συνέχεια την ευκαιρία να ψάξετε, βρείτε, και αγοράσετε άλλα σε αντικατάστασή τους, σας προτείνουμε να αγνοήστε μία ή περισσότερες από τις παρακάτω οδηγίες:-

Στατικός ηλεκτρισμός:

Το σώμα μας και τα ρούχα μας μπορεί να έχουν στατικό ηλεκτρισμό

αρκετών χιλιάδων Volt --έστω και με πολύ μικρά φορτία--

ιδιαίτερα σε ξηρή ατμόσφαιρα

ή όταν φοράμε μάλλινα ρούχα ή παπούτσια με λαστιχένια σόλα·

οι τάσεις αυτές μπορεί να αποβούν ολέθριες γιά τα chips.

Θυμηθείτε πάντα να εκφορτίζεστε πριν ακουμπήσετε τα chips,

ακουμπώντας πρώτα το χέρι σας στην μεταλλική γειωμένη πλάκα

που βρίσκεται αριστερά από την πλακέτα συνδέσεων στη βάση πειραμάτων

(§ 0.4).

-

Διακόπτετε την τροφοδοσία όταν κάνετε συνδέσεις:

πριν κάνετε ή αλλάξετε συνδέσεις,

σβήστε το τροφοδοτικό

προκειμένου να μην υπάρχουν τάσεις στην πλακέτα.

Ανάψτε το τροφοδοτικό μόνον όταν

όλο το κύκλωμά σας είναι εντελώς έτοιμο και σωστό.

-

Προσανατολισμός των chips:

η χαρακτηριστική εγκοπή - σημάδι των chips να είναι πάντα αριστερά,

προκειμένου να μην γίνονται λάθος οι συνδέσεις στους ακροδέκτες τους

(και ιδιάτερα στους ακροδέκτες τροφοδοσίας --σίγουρη μέθοδος καψίματος).

-

Οι ακροδέκτες στραβώνουν εύκολα:

Chips με στραβωμένα ή κομένα ποδαράκια είναι άχρηστα

(και επιβλαβή γιά την πλακέτα συνδέσεων

αν τα ποδαράκια σας κοπούν και μείνουν μέσα).

Η εξαγωγή των chips από την πλακέτα συνδέσεων

(μην τα βγάζετε εσείς, φέτος)

πρέπει να γίνεται

ασκώντας ίση δύναμη από τις δύο πλευρές (αριστερή-δεξιά) του chip,

με το chip αυστηρά οριζόντιο·

αν το τραβήξετε απρόσεκτα θα βγεί πλαγιαστό (αριστερά ή δεξιά),

οπότε σίγουρα θα στραβώσουν τα ακρειανά ποδαράκια του.

Αν δεν έχετε το κατάλληλο εργαλείο εξαγωγής,

βάλτε προσεκτικά ένα κατσαβίδι ή άλλο λεπτό και σκληρό αντικείμενο

κάτω από το chip, χωρίς να γείρει πλάγια το chip,

και μετά ανασηκώστε προσεκτικά το κατσαβίδι,

ισόρροπα από τις δύο πλευρές.

Όταν βάζετε ένα chip, πιέστε το ισόρροπα αριστερά και δεξιά.

Πριν μπορέσει να μπεί το chip,

πρέπει τα ποδαράκια του να ακουμπάνε στο κέντρο των τρυπών της πλακέτας,

και όχι λίγο προς τα έξω (πάνω και κάτω):

σε πολλά chips, ιδιαίτερα όταν είναι καινούργια,

οι δύο σειρές ακροδεκτών (η πάνω και η κάτω)

βρίσκονται σε απόσταση μεταξύ τους

ελαφρώς μεγαλύτερη από την ονομαστική, και γι' αυτό σκαλώνουν

--όλοι μαζί οι ακροδέκτες της μιάς ή της άλλης πλευράς--

στις παρειές των τρυπών της πλακέτας συνδέσεων.

Δεν οφελεί να πιέσετε ένα-ένα τα ποδαράκια

προς τα μέσα με το χέρι,

διότι πρέπει να πιεστούν όλα ταυτόχρονα

και κατά την ίδια μικρή απόσταση.

Βάλτε πρώτα τους ακροδέκτες της μίας πλευράς (π.χ. της επάνω)

να ακουμπήσουν σταθερά στις εισόδους των αντίστοιχων τρυπών,

και στη συνέχεια χρησιμοποιήστε

ένα μικρό χαρακάκι, ή χαρτονάκι, ή πλακίτσα, ή κατσαβίδι,

με το οποίο να πιέστε ελαφρά και ομοιόμορφα προς τα μέσα

όλους μαζί τους ακροδέκτες της άλλης πλευράς,

μέχρις ότου αυτοί να μπούνε από μόνοι τους και χωρίς δύναμη

στις εισόδους των τρυπών.

Μετά, σπρώχνετε από πάνω το chip προς τα κάτω,

ομοιόμορφα στη δεξιά και αριστερή πλευρά.

-

Τροφοδοσία στους σωστούς ακροδέκτες:

κάνετε πάντα στην αρχή και πολύ προσεκτικά

τις σωστές συνδέσεις τροφοδοσίας (γείωση, VDD)

στους σωστούς ακροδέκτες των chips

--έλλειψη ή λανθασμένη τοποθέτηση αυτών

αποτελεί σίγουρο τρόπο να κάψετε τα chips.

- Βραχυκυκλώματα εξόδων πυλών: Τα chips προσπαθούν να δώσουν στις εξόδους των πυλών τους τη σωστή κάθε φορά τάση, σύμφωνα με τις λογικές πράξεις που κάνουν. Αν συνδέστε (λανθασμένα!) δύο εξόδους τη μία με την άλλη (του ίδιου ή διαφορετικού chip), όταν οι πύλες θέλουν να κάνουν την μία έξοδο 0 και την άλλη 1, προσπαθούν αλλά δεν τα καταφέρνουν, αφού οι δύο έξοδοι είναι βραχυκυκλωμένες μεταξύ τους! Το αποτέλεσμα είναι υπερθέρμανση και κάψιμο των chips!

- Βραχυκυκλώματα εξόδου με γείωση ή VDD: Το ίδιο και χειρότερο είναι να συνδέστε μιάν έξοδο πύλης σε μιά τάση τροφοδοσίας (γείωση ή VDD). Αν η σύνδεση είναι με τη γή, όταν η πύλη θέλει να βγάλει 1 προσπαθεί αλλά δεν μπορεί· αν η σύνδεση είναι με το VDD, όταν η πύλη θέλει να βγάλει 0 ομοίως προσπαθεί αλλά δεν μπορεί· και στις δύο περιπτώσεις, έχουμε βραχυκύκλωμα, υπερθέρμανση, και κάψιμο!

-

Βραχυκυκλώματα εξόδου με είσοδο από την πλακέτα εισόδων/εξόδων:

Οι είσοδοι που σας έρχονται

από τους διακόπτες της πλακέτας εισόδων/εξόδων

μέσω της αριστερής καλωδιοταινίας

(§ 2.10)

είναι έξοδοι κάποιας πύλης οδήγησης

που βρίσκεται πάνω στην πλακέτα εισόδων/εξόδων.

Αν βραχυκυκλώστε μιά τέτοια είσοδο προς το κύκλωμά σας

με την έξοδο μιάς πύλης σας,

θα έχετε τα ίδια αποτελέσματα όπως παραπάνω:

όταν οι δύο οδηγητές

(η πύλη σας και ο διακόπτης της πλακέτας εισόδων/εξόδων)

διαφωνούν μεταξύ τους γιά το ποιά είναι η επιθυμητή τιμή

του βραχυκυκλωμένου κόμβου,

θα περνάει πολύ ρεύμα και θα υπερθερμαίνονται, με κίνδυνο καψίματος.

- Ασύνδετη είσοδος ΔΕΝ είναι (αναγκαστικά) μηδέν (0). (Αυτό δεν αποτελεί αιτία καψίματος, αλλά μόνον αιτία να μη δουλεύει σωστά το κύκλωμά σας). Οι είσοδοι των chips CMOS έχουν πολύ μεγάλη (σχεδόν άπειρη) αντίσταση· άρα, αφήνοντάς τις ανοικτοκυκλωμένες (ασύνδετες) παίρνουν τυχαία, απόβλεπτη τάση (τιμή) (δηλ. θόρυβος, σκουπίδια), και όχι αναγκαστικά 0 ή 1, ούτε καν αναγκαστικά τιμή σταθερή στο χρόνο. Οι είσοδοι των chips TTL συμπεριφέρονται παρόμοια, με μία προτίμηση στο 1 αντί του 0 όταν μένουν ανοικτοκυκλωμένες. Συμπέρασμα: όταν δεν χρησιμοποιείτε μιάν είσοδο μιάς πύλης σας και θέλετε η είσοδος αυτή να είναι πάντα 0 (π.χ. είσοδος μιάς πύλης OR), συνδέστε την στη γείωση. Όταν δεν χρησιμοποιείτε μιάν είσοδο και την θέλετε πάντα 1 (π.χ. είσοδος μιάς πύλης AND), συνδέστε την στη θετική τροφοδοσία (VDD). (Εξαίρεση: οι είσοδοι της πλακέτας εισόδων/εξόδων που οδηγούν τις ενδεικτικές LED έχουν ειδικές αντιστάσεις καθέλκυσης πάνω στην πλακέτα αυτή, οι οποίες την κάνουν να βλέπει "0" όταν εσείς τις αφήνετε ασύνδετες).

Πείραμα 3.10: Αποκωδικοποιητής 2-σε-4

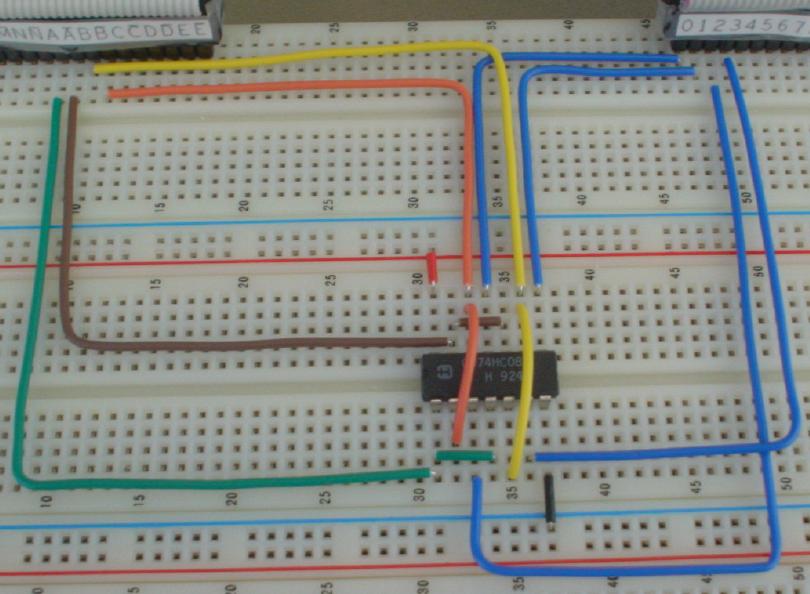

Όπως είδαμε στην § 2.7, ο αποκωδικοποιητής 2-σε-4 είναι ένα συνδυαστικό κύκλωμα δύο εισόδων, ας πούμε A και B, και τεσσάρων εξόδων, όπου οι έξοδοι ακολουθούν τις εξισώσεις: Out0 = (A')·(B'), Out1 = (A')·(B), Out2 = (A)·(B'), και Out3 = (A)·(B). Αυτό ακριβώς το κύκλωμα φαίνεται στο σχήμα,

και η υλοποίησή του με το chip 7408 του προηγουμένου πειράματος

φαίνεται στην φωτογραφία.

Παρατηρήστε ότι εκμεταλλευόμαστε το γεγονός ότι

η πλακέτα εισόδων/εξόδων μας δίνει

όχι μόνο τις θετικές τιμές των διακοπτών εισόδου, π.χ. A και B,

αλλά και τις αρνητικές τιμές (αρνήσεις) τους, A' και B'·

έτσι, δεν χρειαζόμαστε chip 7404 γιά να τις γεννήσουμε.

Κατασκευάστε (με την τροφοδοσία σβηστή όπως πάντα)

το εικονιζόμενο κύκλωμα στο εργαστήριο,

ελέγξτε το, και δείξτε το στον επιτηρητή-βοηθό σας.

Αυτό ακριβώς το κύκλωμα φαίνεται στο σχήμα,

και η υλοποίησή του με το chip 7408 του προηγουμένου πειράματος

φαίνεται στην φωτογραφία.

Παρατηρήστε ότι εκμεταλλευόμαστε το γεγονός ότι

η πλακέτα εισόδων/εξόδων μας δίνει

όχι μόνο τις θετικές τιμές των διακοπτών εισόδου, π.χ. A και B,

αλλά και τις αρνητικές τιμές (αρνήσεις) τους, A' και B'·

έτσι, δεν χρειαζόμαστε chip 7404 γιά να τις γεννήσουμε.

Κατασκευάστε (με την τροφοδοσία σβηστή όπως πάντα)

το εικονιζόμενο κύκλωμα στο εργαστήριο,

ελέγξτε το, και δείξτε το στον επιτηρητή-βοηθό σας.

3.11 Σύνθεση Συνδυαστικών Κυκλωμάτων από τον Πίνακα Αληθείας τους

Συνδυαστικά λέγονται τα ψηφιακά κυκλώματα των οποίων οι έξοδοι είναι συναρτήσεις μόνο της παρούσας τιμής των εισόδων, και όχι οιασδήποτε παρελθούσας τιμής, δηλαδή τα ψηφιακά κυκλώματα που δεν έχουν "μνήμη". Η λογική συμπεριφορά των συνδυαστικών κυκλωμάτων (δηλαδή οι ψηφιακές τιμές των εξόδων τους, αγνοώντας θέματα καθυστέρησης, θορύβου, κλπ) περιγράφεται και προδιαγράφεται πλήρως από τον Πίνακα Αληθείας τους, δηλαδή από τον πίνακα που λέει τι τιμή παίρνουν οι έξοδοί τους γιά καθ' ένα από τους δυνατούς συνδυασμούς τιμών των εισόδων τους. Μέχρι τώρα, οι λογικές συναρτήσεις (AND, OR, NOT) που θέλαμε να υλοποιήσουμε δίνονταν έτοιμες, όπως αυτές προέκυπταν από τη διατύπωση του προς επίλυση προβλήματος. Τώρα θα δούμε τι κάνουμε όταν η διατύπωση του προβλήματος ξεκινά με δοσμένο τον πίνακα αληθείας μόνο, ή όταν επιδιώκουμε την απλοποίηση δοσμένων λογικών συναρτήσεων.

Θα χρησιμοποιήσουμε, αρχικά, το παράδειγμα

συνδυαστικού κυκλώματος δύο εισόδων και επτά εξόδων

που φαίνεται εδώ.

Οι έξοδοι οδηγούν τις 7 φωτοεκπομπούς διόδους της ένδειξης 7 τμημάτων

(§ 2.10),

σε τρόπον ώστε να εμφανίζονται σε αυτήν τα "γράμματα" A, b, c, και d,

όταν οι είσοδοι είναι 00, 01, 10, και 11, αντίστοιχα.

Γιά να επιτευχθούν τα σχήματα αυτά της οθόνης,

πρέπει η κάθε έξοδος να έχει τις τιμές που δείχνει ο παρακάτω πίνακας

στον καθένα από τους 4 συνδυασμούς τιμών των εισόδων·

τιμή 1 προκαλεί άναμα της αντίστοιχης LED,

ενώ τιμή 0 σημαίνει LED σβηστή:

Θα χρησιμοποιήσουμε, αρχικά, το παράδειγμα

συνδυαστικού κυκλώματος δύο εισόδων και επτά εξόδων

που φαίνεται εδώ.

Οι έξοδοι οδηγούν τις 7 φωτοεκπομπούς διόδους της ένδειξης 7 τμημάτων

(§ 2.10),

σε τρόπον ώστε να εμφανίζονται σε αυτήν τα "γράμματα" A, b, c, και d,

όταν οι είσοδοι είναι 00, 01, 10, και 11, αντίστοιχα.

Γιά να επιτευχθούν τα σχήματα αυτά της οθόνης,

πρέπει η κάθε έξοδος να έχει τις τιμές που δείχνει ο παρακάτω πίνακας

στον καθένα από τους 4 συνδυασμούς τιμών των εισόδων·

τιμή 1 προκαλεί άναμα της αντίστοιχης LED,

ενώ τιμή 0 σημαίνει LED σβηστή:

A B a b c d e f g

0 0 1 1 1 0 1 1 1

0 1 0 0 1 1 1 1 1

1 0 0 0 0 1 1 0 1

1 1 0 1 1 1 1 0 1

Αυτό που φτιάξαμε είναι οι 7 πίνακες αληθείας

των 7 συνδυαστικών κυκλωμάτων

που θα παράγουν τις 7 εξόδους a, b, ..., g,

σαν ψηφιακές δυαδικές συναρτήσεις των 2 εισόδων A και B.

Η επόμενη δουλειά μας είναι,

με βάση αυτούς τους πίνακες,

να φτιάξουμε τα αντίστοιχα κυκλώματα,

χρησιμοποιώντας τις λογικές πράξεις

(§ 3.5)

AND, OR, NOT, και τις υλοποιήσεις τους με ηλεκτρονόμους ή chips.

Αυτό θα το κάνουμε εδώ αναγνωρίζοντας,

από τον κάθε πίνακα αληθείας,

τη λογική συνάρτηση που αυτός αναπαριστά·

Προς στιγμήν θα κάνουμε την αναγνώριση αυτή "πρόχειρα",

χωρίς συγκεκριμένη μέθοδο,

και στο επόμενο εργαστήριο θα αναπτύξουμε μιά μέθοδο

που μας επιτρέπει ευκολότερη αναγνώριση "με το μάτι",

γράφοντας τις τιμές της συνάρτησης σ' ένα διδιάστατο πίνακα,

αντί σε μία κατακόρυφη στήλη.

Η πρόχειρη αναγνώριση μας οδηγεί,

στο παράδειγμα εδώ, στις λογικές συναρτήσεις:

- a = A' · B' = (ΟΧΙ A) ΚΑΙ (ΟΧΙ B)

- b = (A' · B') + (A · B) = [(ΟΧΙ A) ΚΑΙ (ΟΧΙ B)] Ή [(A) ΚΑΙ (B)]

- c = A' + B = (ΟΧΙ A) Ή (B)

- d = A + B = (A) Ή (B), f = A' = (ΟΧΙ A)

- e = 1, g = 1

Άσκηση 3.12: Οι Αριθμοί 0-3 στην Οθόνη 7 Τμημάτων

Προδιαγράψτε (μέσω του πίνακα αληθείας του) ένα κύκλωμα ανάλογο αυτού της παραγράφου 3.11, που όμως να εμφανίζει στον ενδείκτη 7 τμημάτων τους αριθμούς 0, 1, 2, και 3, όπως φαίνεται δεξιά, αντί των γραμμάτων A, b, c, και d που ενεφάνιζε το προηγούμενο κύκλωμα. Στη συνέχεια, μελετήστε τους πίνακες αληθείας των 7 εξόδων αυτού του κυκλώματος (δηλαδή τις 7 στήλες του πίνακα αληθείας), και εκφράστε κάθε έξοδο σαν μιά λογική συνάρτηση (όσο απλή γίνεται) των δύο εισόδων A και B.

Πείραμα 3.13: Οι Αριθμοί 0-3 με Πύλες

Υλοποιήστε τις εξισώσεις της παραπάνω άσκησης 3.12 με πύλες AND και OR των chips 7408 και 7432 που έχετε στο σακκουλάκι σας. Η θέση των ακροδεκτών των chips φαίνεται στο σχήμα δεξιά. Πριν το εργαστήριο σχεδιάστε το κύκλωμα με λογικές πύλες AND, OR, NOT της ενότητας § 3.5 (πρώτο σχήμα), σημειώνοντας πάνω σε κάθε ακροδέκτη πύλης AND και OR σε ποιόν αριθμό pin τίνος chip αυτός θα αντιστοιχεί κατά την κατασκευή. Στο εργαστήριο, κατασκευάστε και ελέγξτε το κύκλωμα, και δείξτε το στον επιτηρητή-βοηθό σας. Οι είσοδοί σας τώρα πρέπει να έρχονται από τους διακόπτες της πλακέτας εισόδων/εξόδων, διότι το ανοικτό κύκλωμα των άλλων (σκέτων) διακοπτών όταν αυτοί δεν πατιώνται δεν αποτελεί αποδεκτή είσοδο γιά τα chips (αν επιμένατε να χρησιμοποιήστε απλούς, σκέτους διακόπτες, θα έπρεπε να συνδέστε τις δύο επαφές τους σε γη και τροφοδοσία, και να πάρετε είσοδο στις πύλες από τον πόλο τους). Εκμεταλλευτείτε το γεγονός ότι η πλακέτα εισόδων/εξόδων μας δίνει όχι μόνο τις θετικές τιμές των διακοπτών εισόδου, π.χ. A και B, αλλά και τις αρνητικές τιμές (αρνήσεις) τους, A' και B'· έτσι, δεν χρειαζόμαστε chip 7404 γιά να τις γεννήσουμε. Τροφοδοτήστε με τις 7 εξόδους του κυκλώματός σας τα 7 τμήματα της ένδειξης 7 τμημάτων της πλακέτας εισόδων/εξόδων, όπως και στο προηγούμενο πείραμα 3.12.

|

[Up - Table of Contents] [Prev - 2. Relays] |

[4. Karnaugh, RAM - Next] |

| Up to the Home Page of CS-120 | © copyright

University of Crete, Greece.

last updated: 19 Oct. 2020, by M. Katevenis. |