# 2. Link and Memory Architectures and Technologies

2.1 Links, Thruput/Buffering, Multi-Access Ovrhds

2.2 Memories: On-chip / Off-chip SRAM, DRAM

2.A Appendix: Elastic Buffers for Cross-Clock Commun.

Manolis Katevenis

CS-534 – Univ. of Crete and FORTH, Greece

http://archvlsi.ics.forth.gr/~kateveni/534

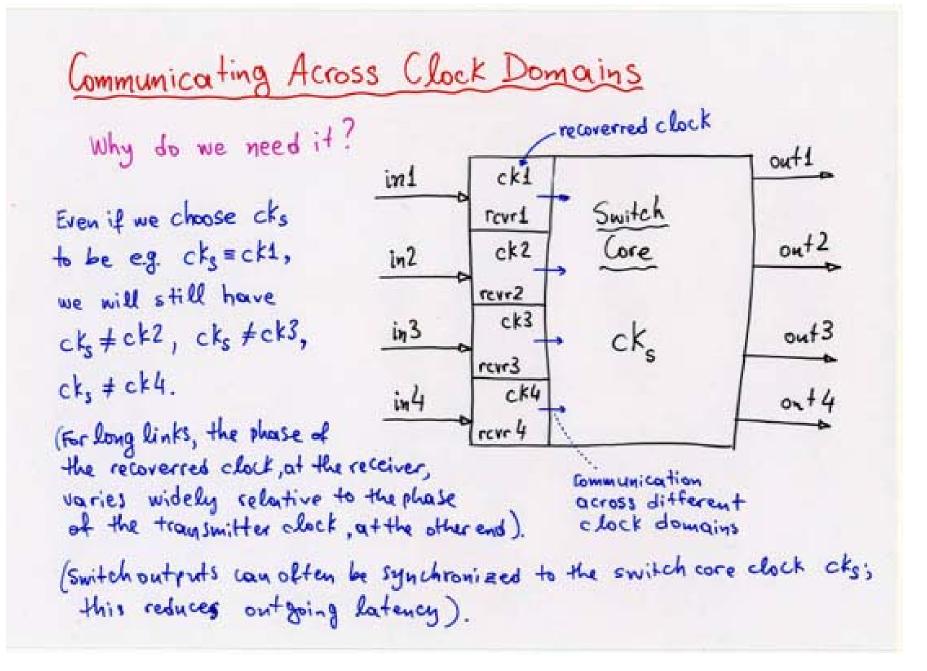

## 2.A Elastic Buffers for Cross-Clock Communication

### Table of Contents:

- Oscillator frequency deviation

- have *idle* symbols in the flow, for removal/insertion at interfaces

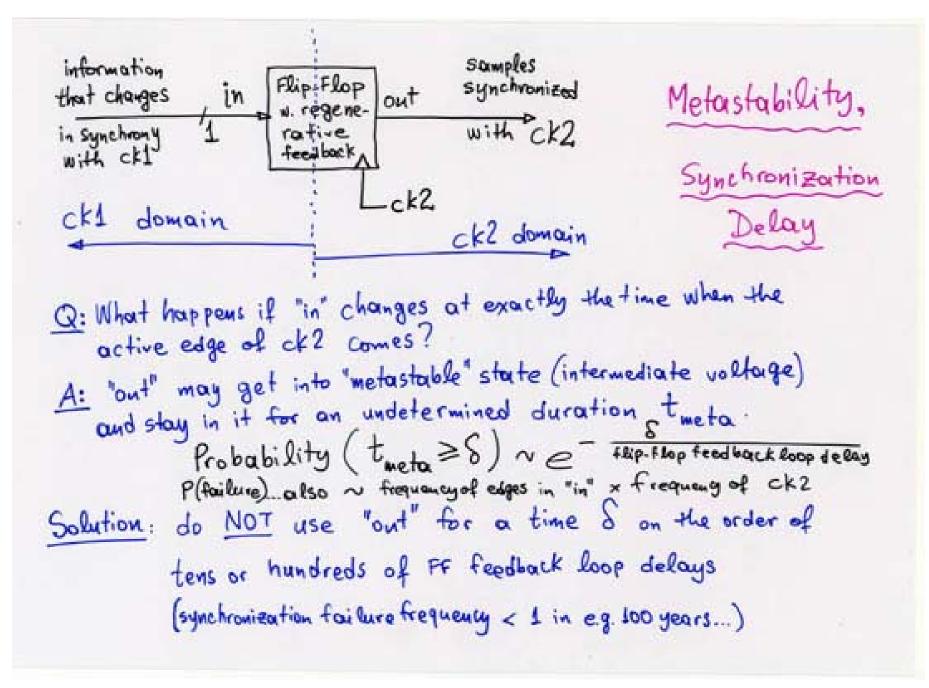

- Single-bit communication

- either 0 or 1 is OK, but *not* intermediate *not metastable*

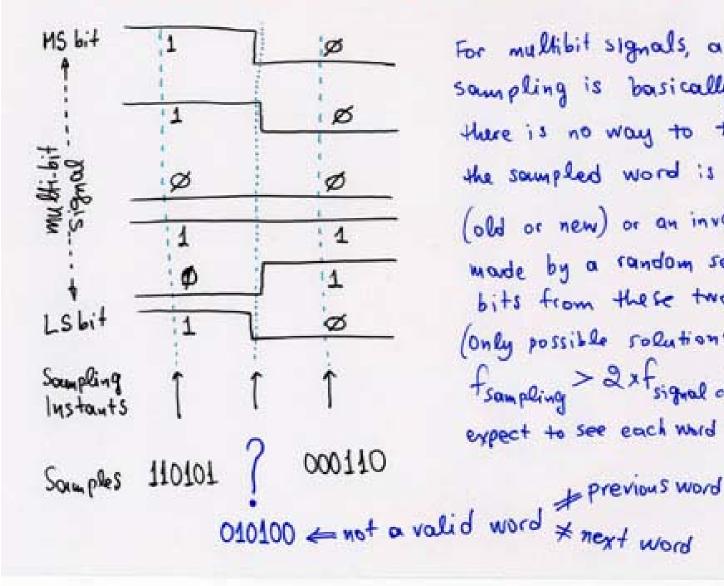

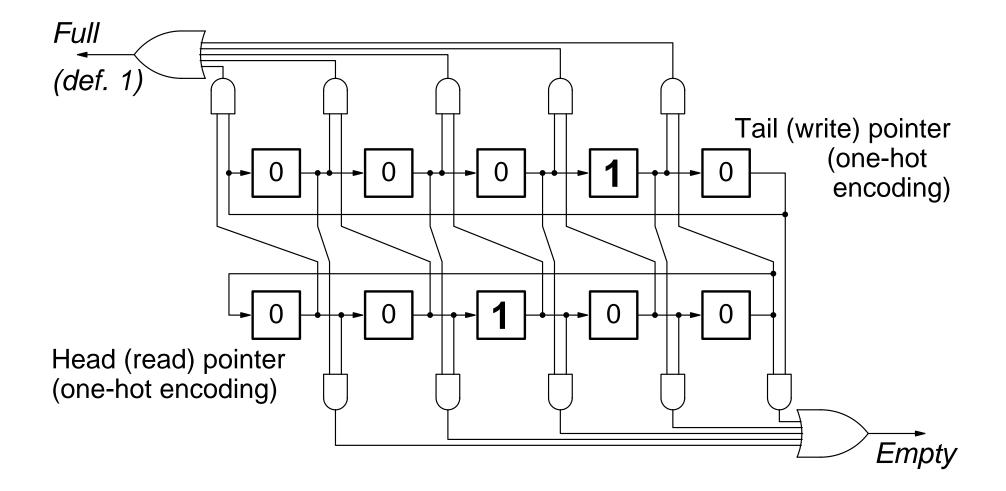

- Multi-bit word communication, at almost 1 word/cycle rate

- can<u>not</u> sample asynchronously to the source clock

- need 2-port FIFO

- read-pointer to write-pointer comparison problem

- synchronizing the empty/full flags leads to low access rate

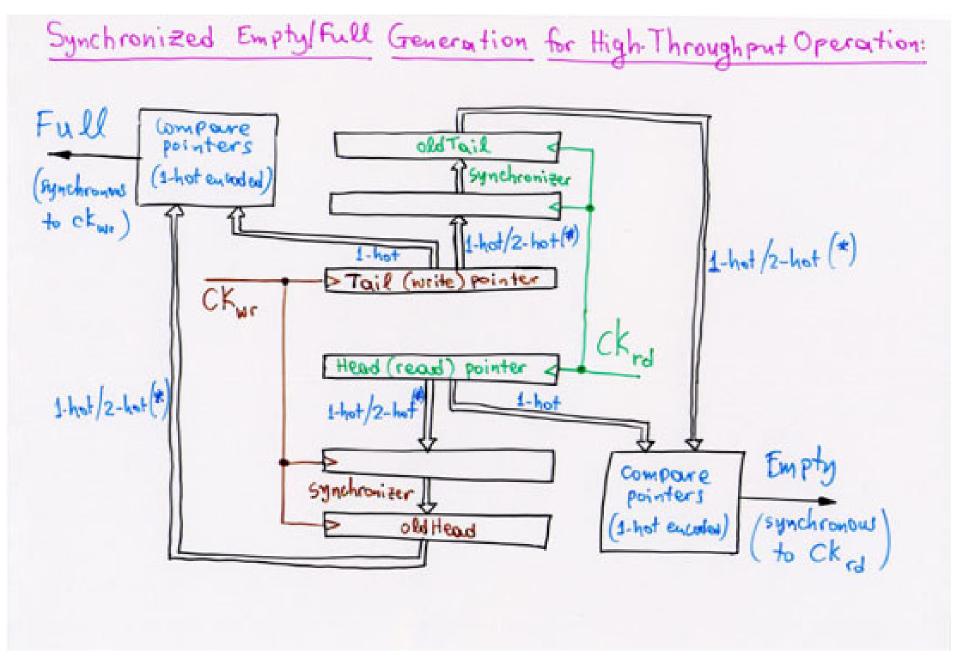

- 1-hot (or 2-hot) encoding; compare to an old, conservative, synchronized version of the other-domain's pointer

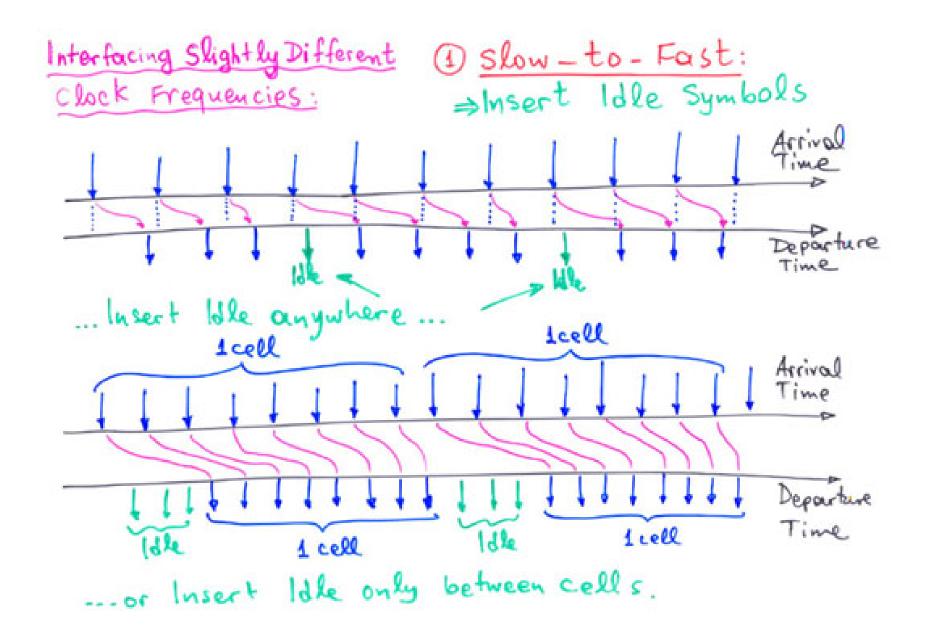

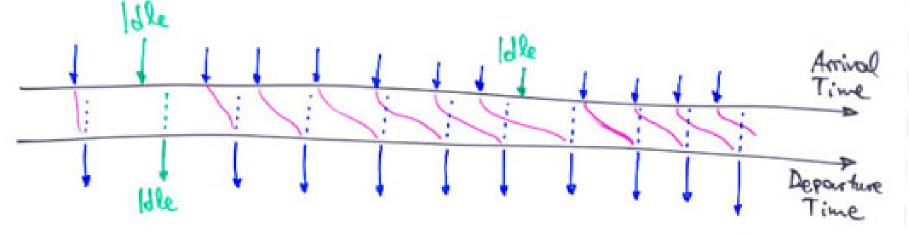

Interfacing Slightly Different Clock Frequencies:

(2) Fast-to-Show:

(α) ⇒ Remove Idle Symbols

and/or (B) => notify the transmitter, by feedback ("backpressure") to slow down or wait, i.e. to insert more idle's (so that they can be removed)...

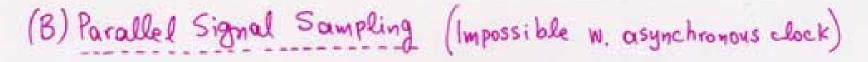

Was the Signal Sampled before or after its Change? (A) Serial Signal Sampling: (Need frameling > frignal change ) in order to "see" all signal changes) Asynchronous Signal: Sampling Instants: Samples: Since the signal changes asynchronously to the sampling clock, the sampling point "?" could have been a little before or a little after the signal changes, yielding either Ø or 1. Hence, it does not matter if the FF metastability eventually yields & or 1 - all that matters is that it becomes a valid binary value, that all of its receivers interpret in the same way.

For multibit signals, asynchronous sampling is basically useless: there is no way to tell if the sampled word is a valid one (old or new) or an invalid word made by a random selection of bits from these two words. (only possible solution: frampling > 2xfrigral change, then expect to see each word twice or more ... )

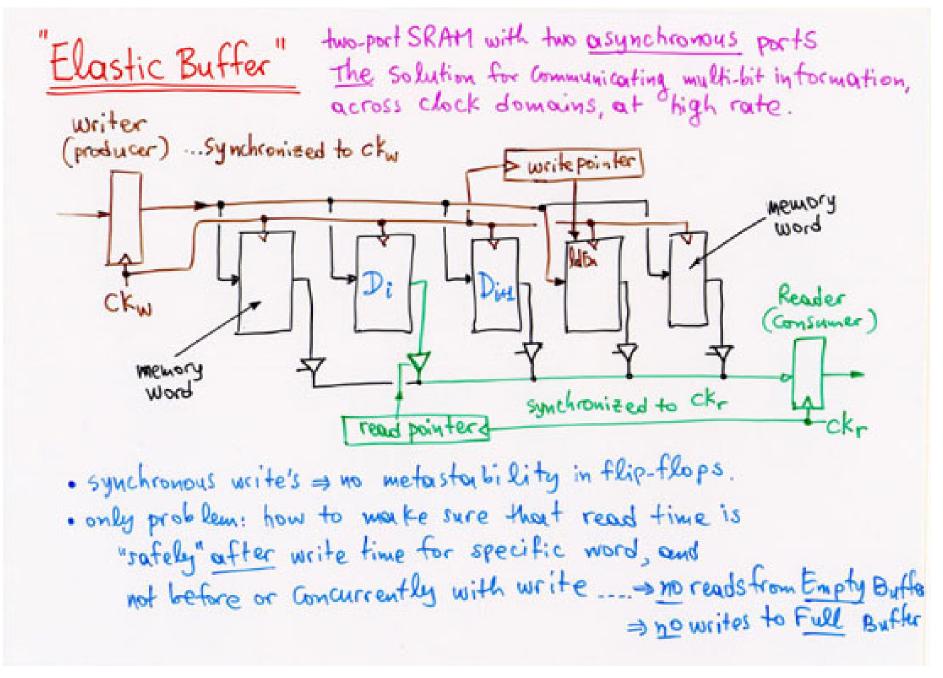

#### **Reminder: Circular Array Implementation of FIFO Queue**

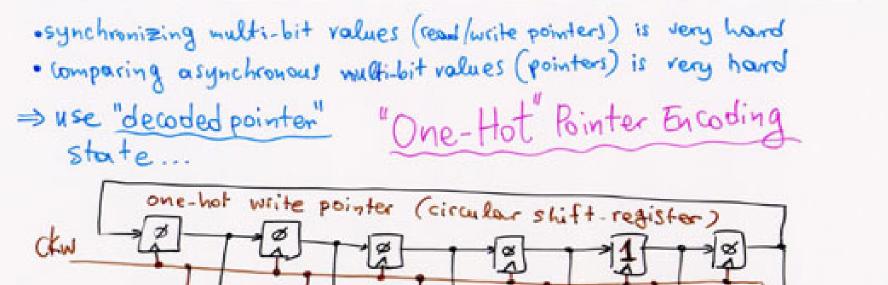

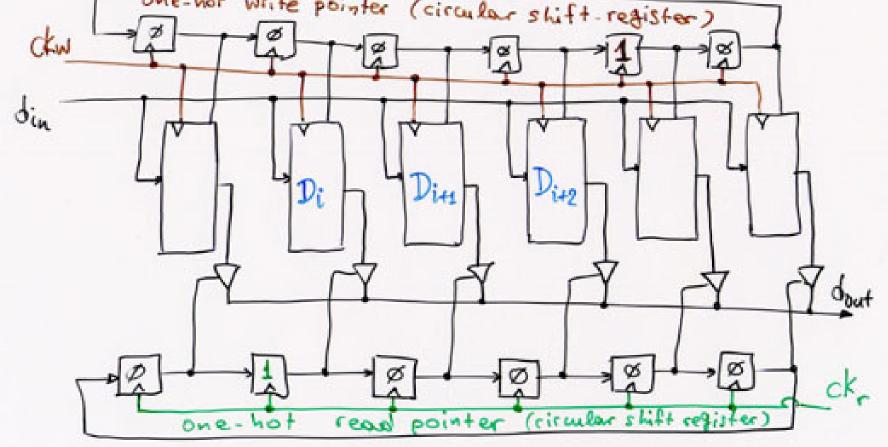

#### **Empty/Full FIFO Detection using One-Hot Pointer Encoding**

Timing & Synchronicity of Full & Empty Flags

- Full flag Synchronous to ckwr

- asserted as soon as a write op. fills the FIFO up (def.1 "full")

- negated after a word is read from the FIFO <u>and</u> the synchronization delay elapses

- <u>Empty</u> flag Synchronous to ck<sub>rd</sub>

- -asserted as soon as a read operation empties the FIFO

- negated after a word is written into the FIFO <u>and</u> the synchronization delay elapses

- <u>Reference</u> on Synchronization and Elastic Buffers: *W. Dally, J. Poulton: "Digital Systems Engineering"*, Cambridge University Press, 1998, ISBN 0-521-59292-5 (sections 10.2 and 10.3 –especially 10.3.4.2).

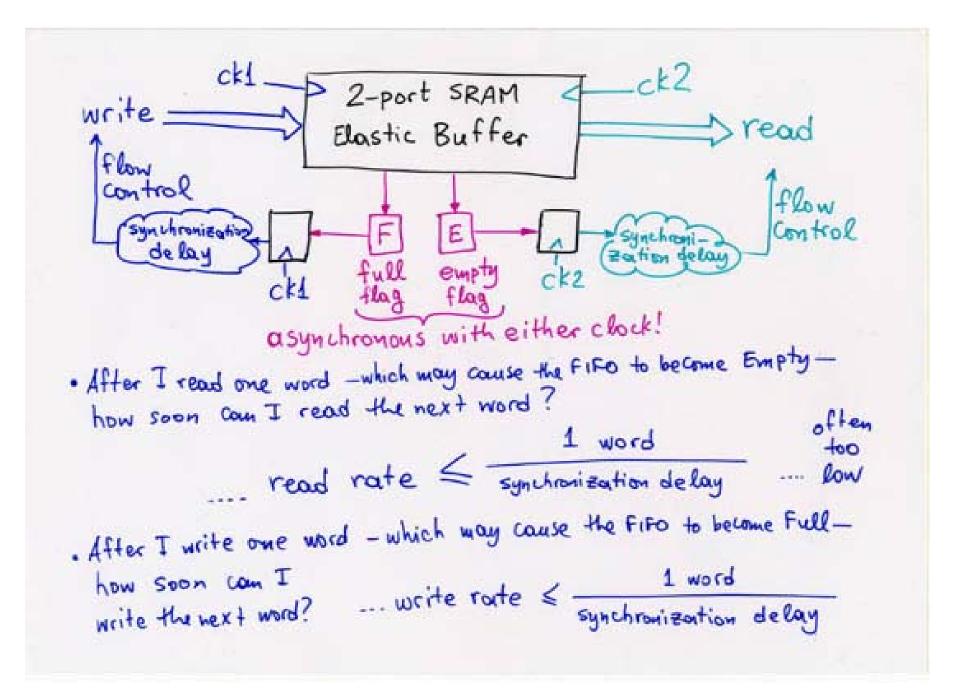

## Sampling 1-hot pointers for synchronization purposes: 1-hot/2-hot versions

- A 1-hot encoded pointer is a <u>multi-bit value</u>.

- When sampling any such value with an asynchronous clock for synchronization purposes, there is always the possibility that some bits are sampled "before" and some "after" they transition.

- This may result in the sampled pointer containing 2 bits ON, or 1 bit ON, or no bit ON (2-hot, or 1-hot, or 0-hot).

- 2-hot is "OK": <u>conservative</u>!

- 1-hot is normal.

- <u>0-hot is bad</u>: empty/full is not asserted even when the FIFO is in one of these states → we have to <u>ensure</u> that 0-hot <u>never happens</u>!

- ⇒ Use a 1-hot/2-hot version of the pointer for synchronization purposes: make sure that the new "hot" bit is turned ON safely before the old "hot" bit is turned OFF (e.g. use appropriate OR function of master & slave flip-flops).