## 2. Link and Memory Architectures and Technologies

2.1 Links, Thruput/Buffering, Multi-Access Ovrhds

2.2 Memories: On-chip / Off-chip SRAM, DRAM

2.A Appendix: Elastic Buffers for Cross-Clock Commun.

Manolis Katevenis

## CS-534 - Univ. of Crete and FORTH, Greece

http://archvlsi.ics.forth.gr/~kateveni/534

Table of Contents:

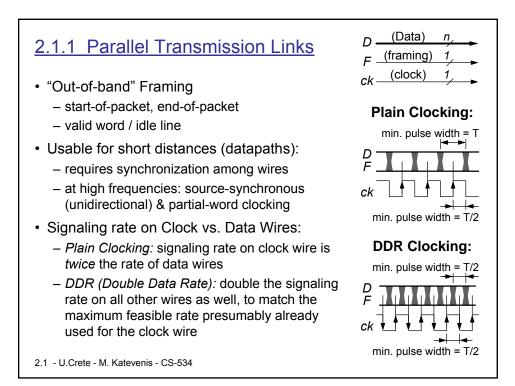

- 2.1.1 Rate, Throughput, Buffer Space, Serial Parallel

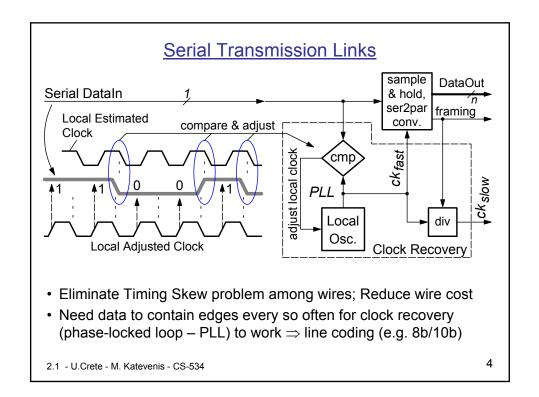

- Parallel and Serial Transmission Links

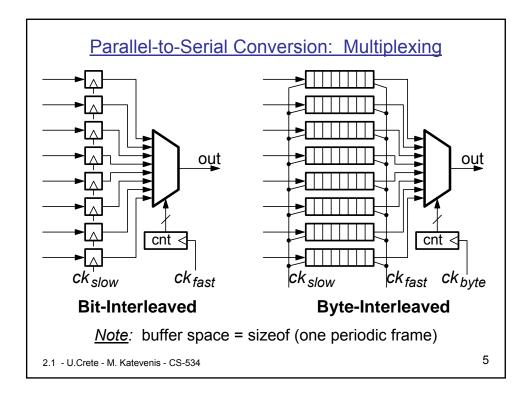

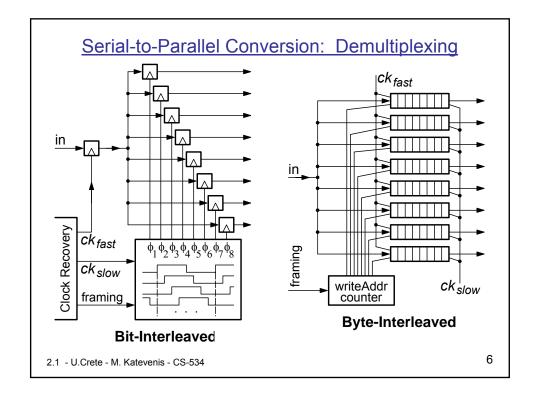

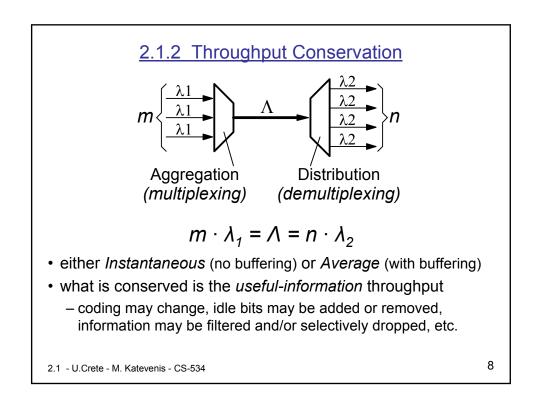

- Parallel-Serial Conversion: Multiplexing, Demultiplexing

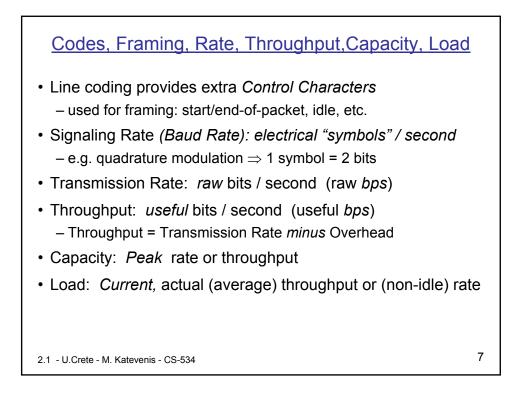

- Rate, Throughput, Capacity, Load

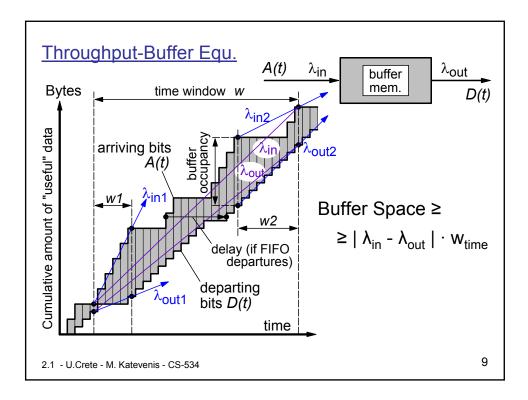

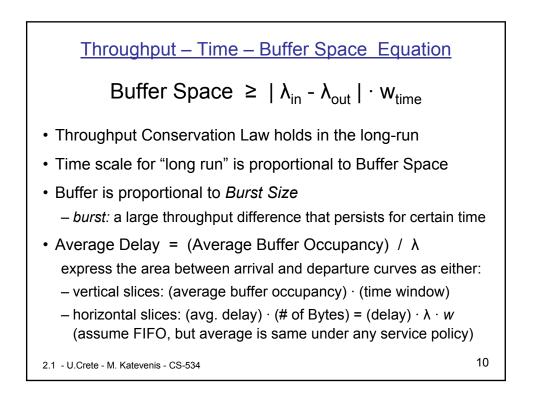

- 2.1.2 Throughput Time Buffer Space Equation

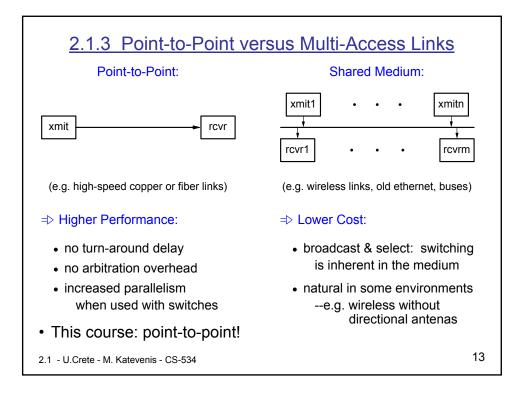

- 2.1.3 Point-to-Point versus Multi-Access Links

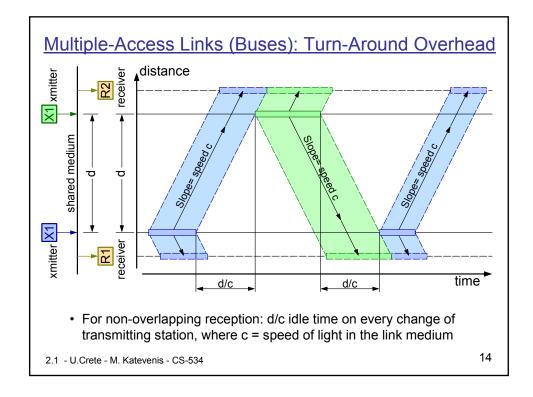

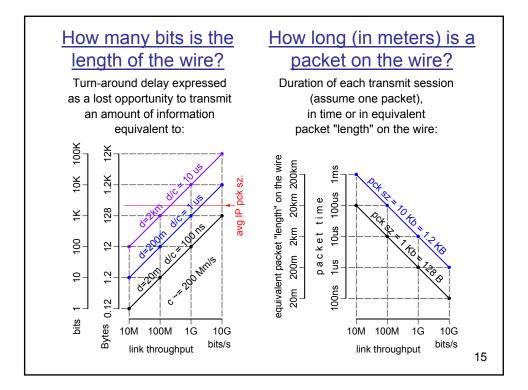

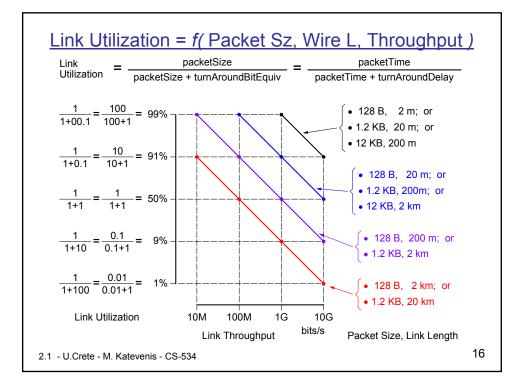

- Turn-around Overhead, Link Utilization

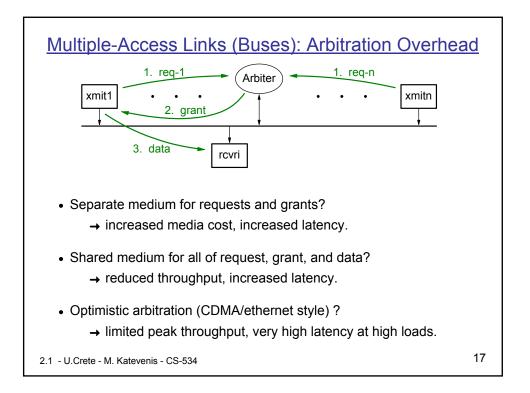

- Arbitration Overhead

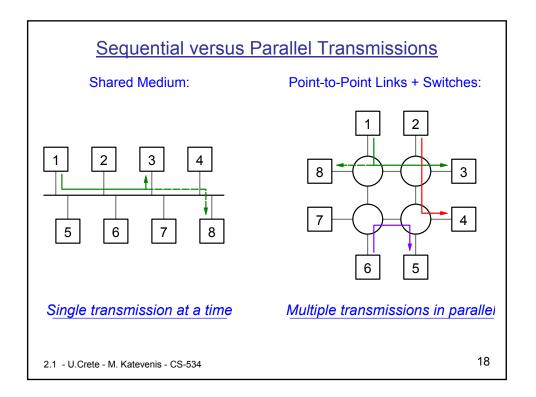

- Sequential versus Parallel Transmissions

2.1 - U.Crete - M. Katevenis - CS-534

2

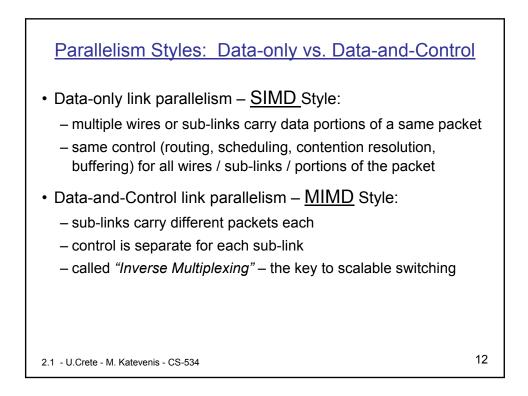

| Parallel Link Forms / Concepts        |                 |                      |               |

|---------------------------------------|-----------------|----------------------|---------------|

| Bit                                   | Cell-Slice      | Packet               | Flow          |

| bit 1 of 8                            | By. 1-8         | packet 1             | flow 1        |

| bit 2 of 8                            | By. 9-16        | packet 2             | flow 2        |

| bit 3 of 8                            | By. 17-24       | packet 3             | flow 3        |

| bit 4 of 8                            | By. 25-32       | packet 4             | flow 4        |

| bit 5 of 8                            | By. 33-40       | packet 5             | flow 5        |

| bit 6 of 8                            | By. 41-48       | packet 6             | flow 6        |

| bit 7 of 8                            | By. 49-56       | packet 7             | flow 7        |

| bit 8 of 8                            | By. 57-64       | packet 8             | flow 8        |

| of 64B cell                           |                 | Inverse Multiplexing |               |

| same handling for all wires           |                 | different handling   |               |

| (same time, sa                        | me destination) | (diff. times &       | destinations) |

| 2.1 - U.Crete - M. Katevenis - CS-534 |                 |                      |               |