# **CS-534**

# **Packet Switch Architecture**

The Hardware Architect's Perspective on High-Speed Networking and Interconnects

*Manolis Katevenis* University of Crete and FORTH, Greece

http://archvlsi.ics.forth.gr/~kateveni/534

# 1. Basic Concepts and Queueing Architectures

#### Table of Contents:

#### • 1.1 Problem Statement

- scalable, distributed, multi-party communication

## • 1.2 Basic Concepts and Terminology

- feasible traffic, internal blocking

- output contention, buffering, flow control, admission control

- circuit versus packet switching

- time vs. space switching, multiplexor, crossbar, buffer memories

#### • 1.3 Queueing Architectures – Family 1:

- shared buffer, output queueing, crosspoint queueing

- 1.4 Queueing Architectures Family 2:

- input queueing: head-of-line blocking, per-output queues

#### 1.1 Problem Statement

Scalable, Distributed, Multi-party Communication

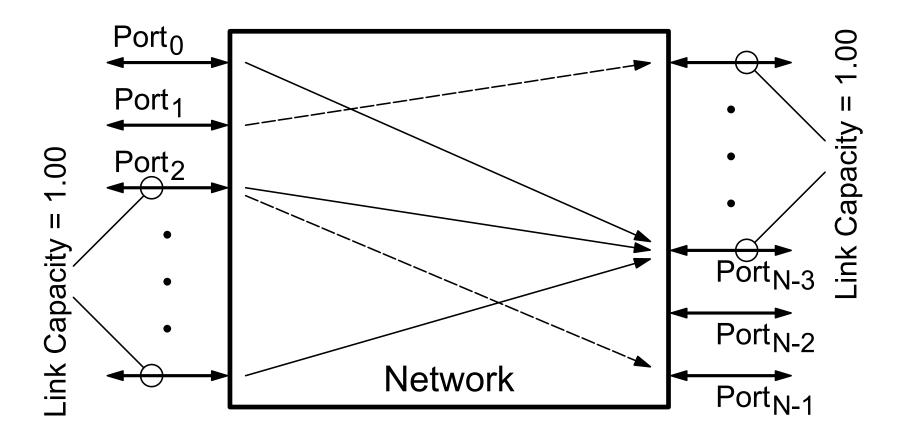

**<u>Output Contention</u>**:  $\sum$  incoming rates > outgoing link capacity

#### 1.1 Problem Statement

#### Scalable, Distributed, Multi-party Communication

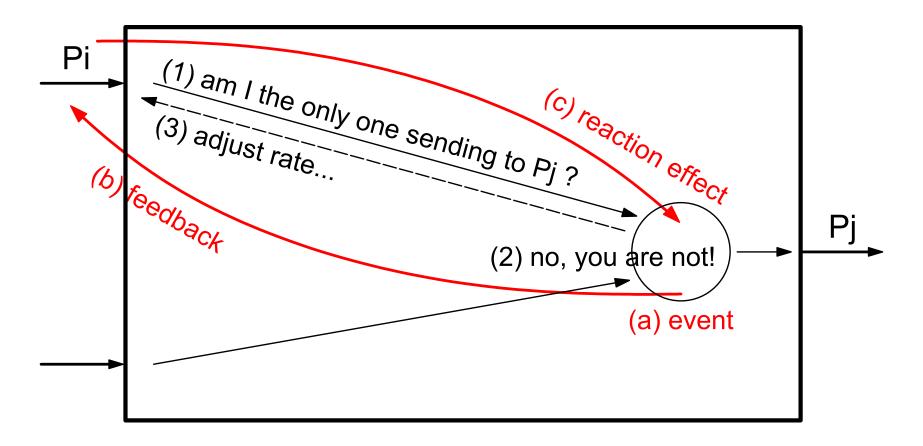

Reaction Effect Delay = Round-Trip Time (RTT)

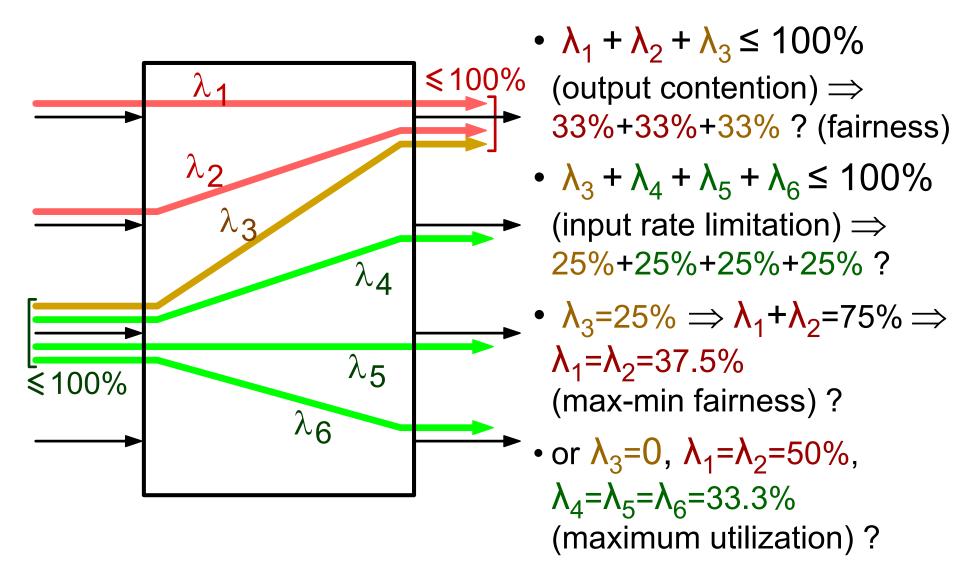

## Example: Interdependent Constraints

#### 1.1 Problem Statement

## Scalable, Distributed, Multi-party Communication

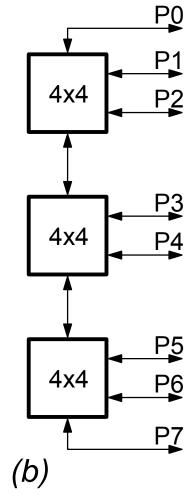

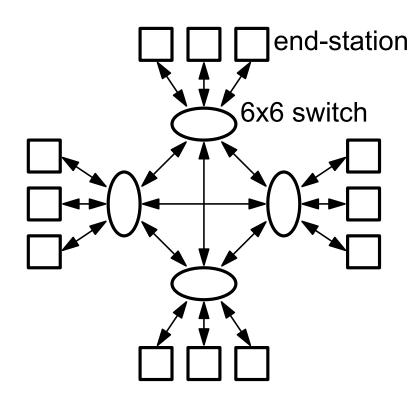

- (a) all-to-all connectivity costs O(N<sup>2</sup>)

- (b) lower-cost scalability is feasible – with or without compromise on performance?

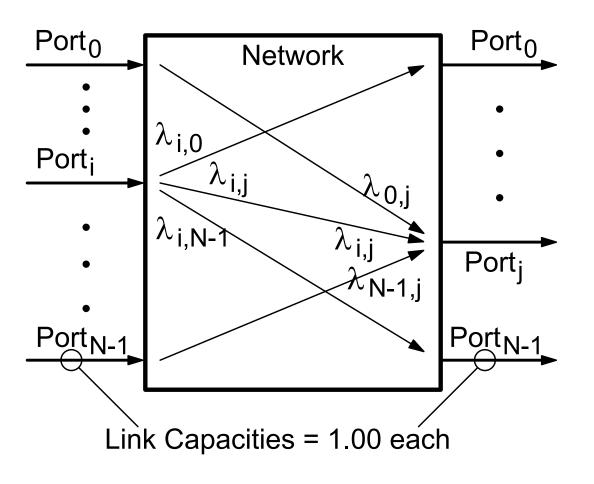

#### 1.2 Basic Concepts & Terminology: Feasible Traffic

• Rates satisfying:

•

$$\forall i: \sum_{j} \lambda_{i,j} \leq 1$$

, i.e.

do not violate

input link capacities;

and:

- $\forall j: \sum_{i} \lambda_{i,j} \leq 1$ , i.e. do not violate output link capacities – do not create *"output contention"*.

- Flow control & congestion management strive to determine and enforce feasible rates at the sources not at all an easy problem...

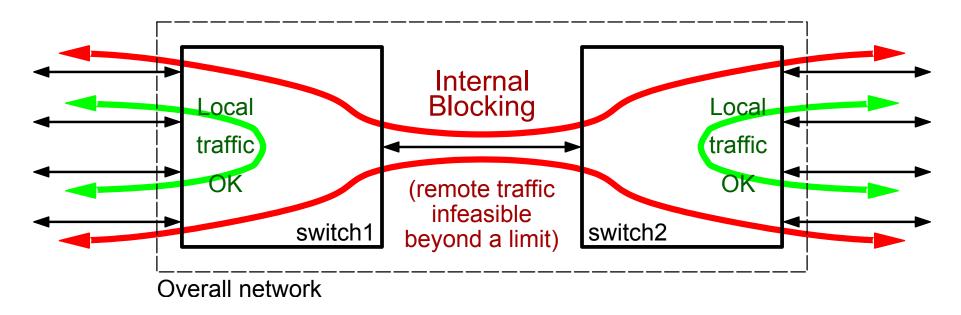

#### 1.2 Basic Concepts & Terminology: Internal Blocking

- Externally feasible traffic for overall network, but...

- Internally not feasible, due to internal link oversubscription.

- Int. blocking in a network is output contention in a subnetwork, but:

- Output contention is the customer's responsibility, while...

- Internal blocking is the network provider's responsibility.

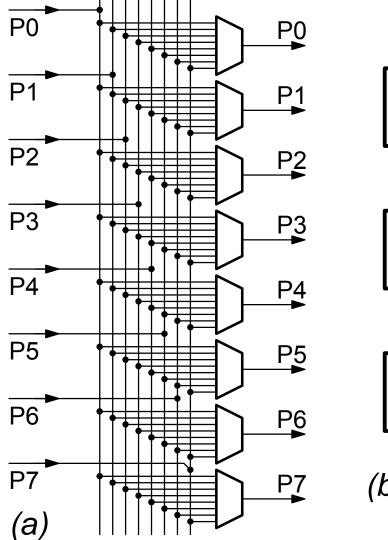

Internal Blocking: a quiz and a preview of a key Result

- does this network have internal blocking?

- (a)... if each flow is always routed through a fixed path?

- (b)... if routing paths can adapt to traffic patterns?

- hint: consider the traffic crossing a 45° bisection ("bisectional throughput")

<u>Key Result</u> (see later): A *NxN* network made of (*N*/2)·log<sub>2</sub>*N* or less 2*x*2 switch elements will *always* have internal blocking. The Benes network, using multipath routing, has  $\approx N \cdot \log_2 N$ 2*x*2 switch elements and is internally non-blocking.

# Dealing with Contention for Link Throughput

- Option 1: Ensure contention never appears

- preschedule everything fixed-rate traffic "circuit switching"

- Option 2: Allow dynamicly varying rates "packet switching"

- 2(a): Dealing with **<u>Short-term</u>** contention

- $\Rightarrow$  manageable volume of excess traffic  $\Rightarrow$  either:

- *buffer* excess packets, temporarily, in memories, or:

- <u>drop</u> excess packets and possibly retransmit later

- OK in some applications, and if we ensure it rarely happens, e.g. if it only happens on memory overflow, or w. massive overspeed

- 2(b): Dealing with Long-term contention

- $\Rightarrow$  unmanageable volume if excess traffic allowed to persist

- either, beforehand, use <u>admission</u> control

- increased latency before traffic allowed to start or change rate

- or, after-the-fact, use <u>flow control congestion</u> management – need large (RTT) buffer space(s) and multiple queues

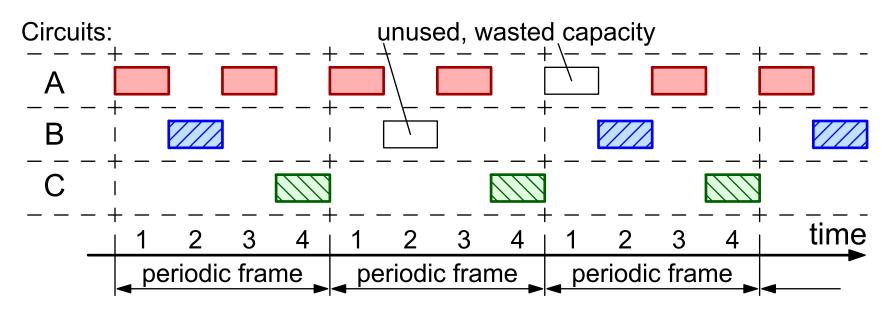

#### 1.2 Basic Concepts & Terminology: Circuit Switching

- Originates from telephonic circuits, digitized and time-multiplexed

- Fixed-rate, prescheduled at connection set-up time like trains

- Data-only no headers needed: time-slot position in frame implicitely provides circuit ID (flow ID) and routing information

- + Simplicity: static, off-line routing decisions and contention resolution

- Partitioned Capacity: throughput is statically partitioned among circuits: unused capacity in one circuit is wasted – cannot be used by other ckts

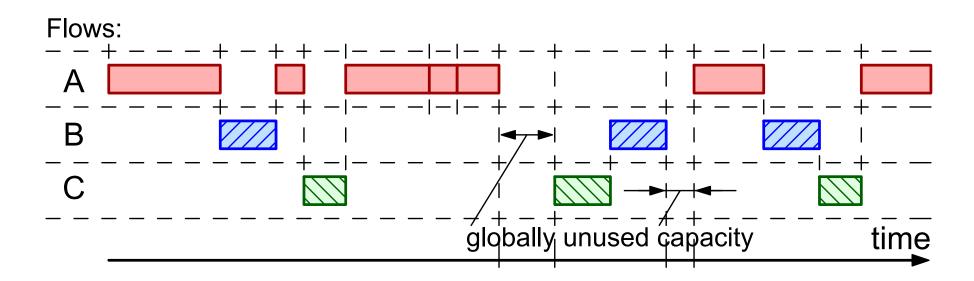

1.2 Basic Concepts & Terminology: Packet Switching

- Varying or unpredictable traffic like automobiles

- Self-describing packets: header provides destination address

- + Transmission capacity of link is dynamically shared among flows

- Demanding: *dynamic, on-line, run-time* routing decisions and contention resolution

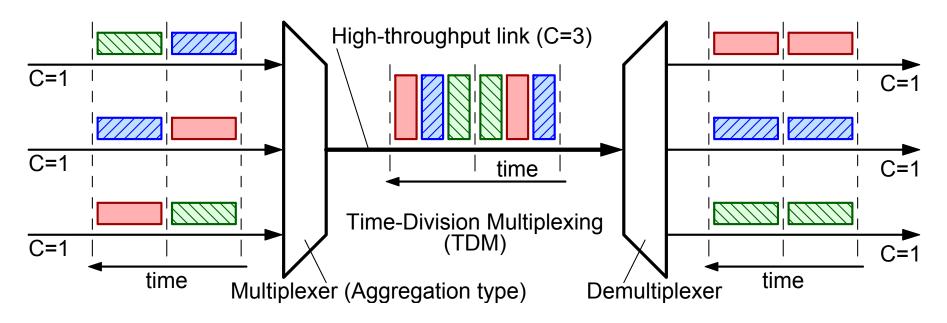

#### 1.2 Basic Concepts & Terminology: Time Switching

- All packets pass through a *single point* in space, at *different times*

- Similar to time-sharing multiprogramming on a single processor

- Buses are in this category (distributed multiplexor, built w. tristate drivers)

- + Economize on datapaths, wires, memories

- + Easy to share aggregate capacity among competing flows

- Non-scalable: infeasible beyond technology limit for aggregate capacity

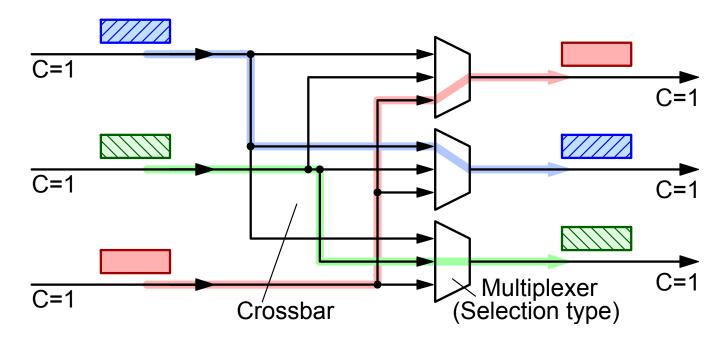

1.2 Basic Concepts & Terminology: Space Switching

- Packets at a given time pass through *different paths in space*

- Similar to multiprocessing on parallel processors

- Crossbars are in this category (single-stage space switches)

- + Scalable: use when aggregate throughput > upper limit of time switching

- Partitioned memories, wires  $\Rightarrow$  harder to route, schedule, load balance

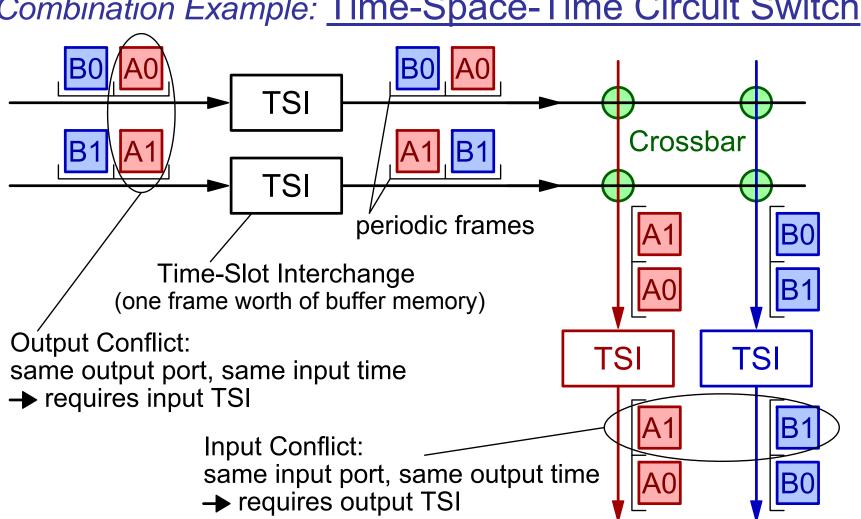

Combination Example: <u>Time-Space-Time Circuit Switch</u>

• Time switching (TSI's) needed to resolve output and input conflicts

# Contention Resolution: Buffer Memories

Memories are needed to temporarily buffer packets that cannot proceed due to (hopefully short-term) output contention

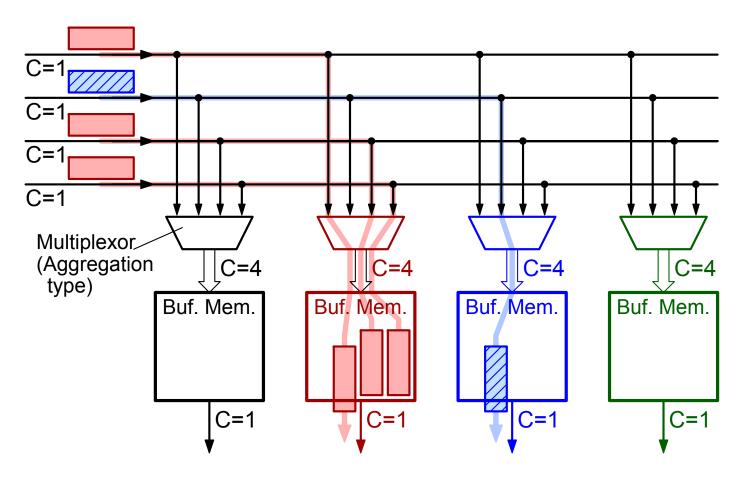

## 1.3 Queueing Architectures – family 1 Output Queueing – the "reference" architecture

- Packets are buffered in peroutput memories, right next to their desired output

- $\Rightarrow \frac{"Work \ Conserving"}{Operation:} an \ output \ will$  $never remain \ idle \ while$ even a single packetdestined to it exists in some $switch buffer memory <math>\Rightarrow$

- + Minimum possible delay

- C=1 C=1 C=1  $\overline{C=1}$ Multiplexor. (Aggregation C=4 C=4 C=4 C=4 type) Buf. Mem. Buf. Mem. Buf. Mem. Buf. Mem. C=1 C=1 C=1 C=1

- + Full (100%) utilization of outgoing link capacity

- + Adaptable to any quality-of-service (QoS) policy: organize queues and scheduler as desired within each per-output buffer; but...

- Wasteful in buffer-memory throughput see shared buffer arch, below

- Partitioned buffer space is less efficient than shared see below...

### <u>Shared Buffer – the "best" architecture</u> (when feasible)

+ Aggregate memory throughput =  $2 \cdot N$ , versus  $N \cdot (N+1) = N^2 + N$  for Outp.Q

- + Same high performance & minimum delay as Outp.Q with proper data str.

- + Shared buffer space is more efficiently used than partitioned in Outp.Q'ng

- Non-scalable: requires building a buffer memory with throughput =  $2 \cdot N$  (Outp.Q'ng is not scalable either: requires mem's of thruput (N+1) each)

# Memory Throughput determines Feasibility & Cost

- Is memory thruput arbitrarily scalable by increasing its width?

- Not for memory widths exceeding the packet size!

- Multi-packet-wide memories are in reality full-fledged switches

- Example: Internet traffic consists of ~ 60% min-size packets, of size 40 Bytes (320 bits) each; assume mem. cycle time = 2 ns ⇒ peak memory thruput = 500 Maccesses/s = 500 Mpackets/s = 500 M × 320 bits/s = 160 Gbps; for 10 Gbps links, this allows the shared buffer arch. to scale only up to 2·*N*=16 ⇒ 8×8 switch

- On-chip memory: power consumption ~ throughput

- e.g. 130 nm  $\Rightarrow$  ≈ 1.5 to 2 mW / Gbps (for small mem. blocks: consumption dominated by sense amp's; large blocks: by size)

- Off-chip memory: wire, pin, and chip count ~ throughput

- RAM chip address and data throughput ≈ 500 to 800 Mbps/pin

- pin & wire count determine pckg size, board area, power cons.

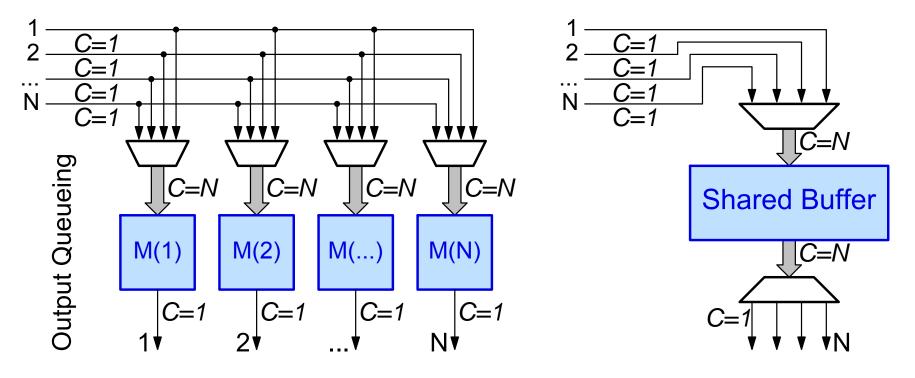

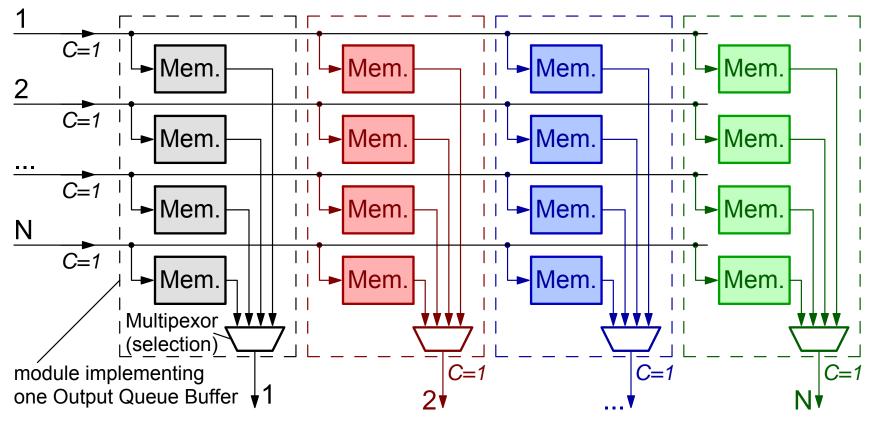

<u>Crosspoint Queueing</u> – scalable but very costly impl. of OQ

- + Same high performance & minimum delay as Output Q'ng or Shared Buf.

- + Scalable: each memory needs throughput of only 2, *independent of N*

- *Very* expensive: total memory thruput =  $2 \cdot N^2$ , versus  $2 \cdot N$  for shared buf.

- Highly partitioned memory: very poor buffer space utilization

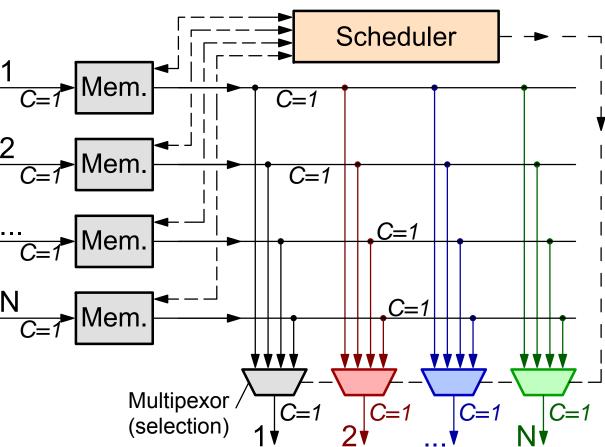

## 1.4 Queueing Architectures – family 2 Input Queueing – the "practical" architecture

- Per-input buffer memories

- + Scalable: each memory needs throughput = 2

⇒ feasible independ. of N

- + Low cost: total memory thruput = 2·N

– same as shared buffer

- Performance suffers a lot, unless *(i)* multiple queues per input, and *(ii)* sophisticated scheduler, and usually *(iii)* other modifications to be seen later (small crosspoint Q's, or internal speedup and OQ's)

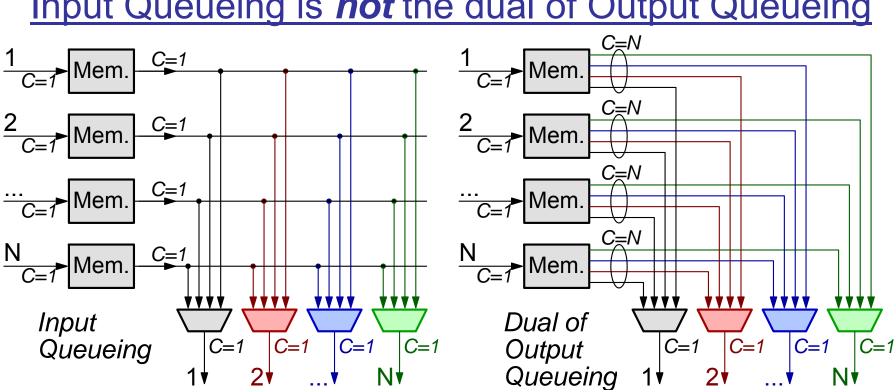

Input Queueing is *not* the dual of Output Queueing

- **Asymmetry** between packet arrival and packet departure conflicts:

- Simultaneous **arrivals** may conflict with each other (packets destined to the same output), and the switch is *obliged to accept* them.

- Simultaneous **departures** are <u>scheduled</u> by the switch  $\Rightarrow$  can be made to *not* originate from the same input – albeit at potential performance cost.

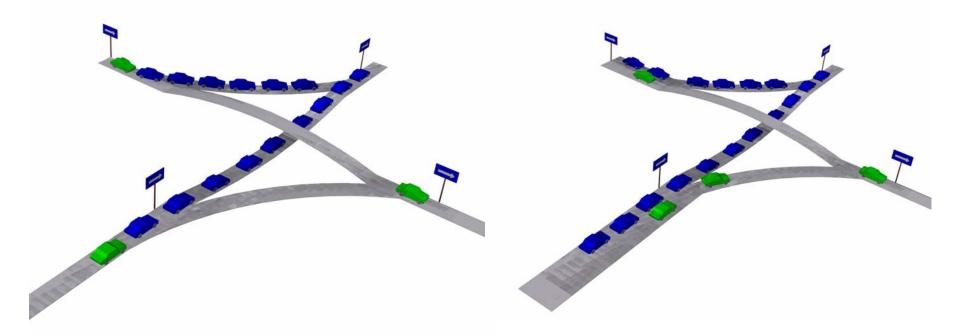

# Head-of-Line (HOL) Blocking

Whenever one First-in-First-Out (FIFO) queue feeds multiple destinations, beware of the danger of head-of-line (HOL) blocking

(called HOL-blocking when bottleneck is the FIFO organization – *not* when other bottleneck, e.g. memory read throughput or output port throughput)

## Multiple Lanes needed to resolve HOL blocking

- As with cars in the road network, HOL blocking spreads the negative effects of congestion (blue cars) to other, unrelated traffic (green cars)

- Multiple "lanes" (queues, virtual circuits) (as many as the congested destinations???) can resolve this problem when properly architected (when packets heading to a common congestion point are prevented from occupying more than one lane) – how should we do this?...

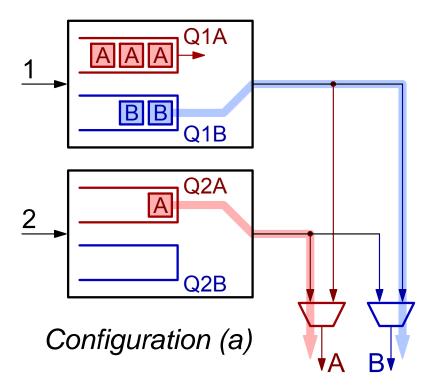

# Crossbar Scheduling with Multiple Queues is tricky

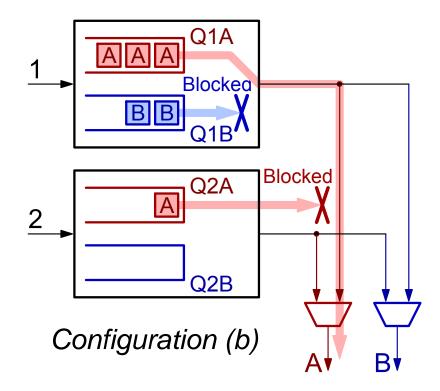

Per-output queues at the inputs avoid HOL blocking – (a): even if Q1A cells are older, the younger Q1B cells can bypass them, since they reside in a separate Q and the scheduler can see them.

- Which of the two configurations should the scheduler choose?

- *(a)* for higher aggregate thruput?

- ... but then, flow Q1A will starve!

# <u>Summary of Queueing Architectures – N×N switch</u>

| Archi-<br>tecture   | per-mem<br>thruput | num.of<br>mem's | tot.mem<br>thruput | mem.sp<br>utilizatn | Perfor-<br>mance | Com-<br>plexity        | Con-<br>clusions      |

|---------------------|--------------------|-----------------|--------------------|---------------------|------------------|------------------------|-----------------------|

| Shared<br>Buffer    | 2·N                | 1               | 2·N                | best                | best             | multiple<br>queues     | best if<br>feasible   |

| Output<br>Q'ing     | N+1                | Ν               | N <sup>2</sup> +N  | medium              | best             | simple                 | refer'nc<br>only      |

| Crosspt<br>Q'ing    | 2                  | N <sup>2</sup>  | 2·N <sup>2</sup>   | worst               | best             | simple                 | simple<br>scalable    |

| Inp.Q<br>singleQ    | 2                  | Ν               | 2·N                | medium              | worst            | simple                 | simple,<br>poor perf  |

| Inp.Q<br>multiQ     | 2                  | Ν               | 2·N                | medium              | medium           | multiQ's,<br>schedul'r | textbook<br>only      |

| Variants<br>(later) | 2 to 4             | 2·N++           | 4·N to<br>8·N++    | medium              | very<br>good     | multiQ's,<br>schedul'r | practical<br>scalable |

1.3 - U.Crete - M. Katevenis - CS-534